CHIPWORKS SEES UMC'S DIFFERENT APPROACH TO 90NM TECHNOLOGY. IS IT 90NM?

OTTAWA, CANADA, May 25th, 2004 - Chipworks Inc. ("Chipworks") the standard setting supplier of reverse engineering services, announced today that they are analyzing the Xilinx XC3S200 Spartan-3 FPGA. Findings indicate a discrepancy in reported process techniques.

Xilinx publicized their move to 90nm technology over a year ago, stating that the Spartan-3 product would be made in both the IBM and UMC foundries on 300 mm wafers. The device analyzed matches UMC's publicity and previous product investigated by Chipworks. It uses seven layers of copper, and one aluminum layer. Xilinx is using the 90nm technology to drive their target pricing down to under $12 for a one-million-gate FPGA and $2.95 for a 50,000 gate FPGA (approximately 17,000 and 1,700 logic cells respectively).

According to Dick James, a senior technology analyst for Chipworks, "we found transistor gate lengths less than 70nm, and a metal 1 (M1) pitch of ~250nm. While these do not meet the letter of the ITRS (International Technology Roadmap for Semiconductors) definition of 90nm feature sizes, they are in the range of 90nm processes announced by other companies. For example, Chipworks measured Texas Instruments' M1 pitch as 300nm and gate length as 48nm, and Intel's M1 pitch is 230nm and gate length is 45nm. ITRS sets the dimensions at 214nm and 37nm, respectively."

UMC's different and more conservative approach for the Xilinx chip lies in the dielectric layers used in the interconnect structure. SIMS analysis shows that the intermetal dielectrics (IMDs) are FSG (fluoro-silicate glass), with undoped glass at the top level. The copper metal is dual damascene, and no trench etch-stop layers have been used, therefore minimizing the effective k-value of the combined dielectric and metal-cap layers.

James stated, "this is the first part that Chipworks has seen that is claimed to be 90nm and is still using only the FSG that is universal in 130nm processes. Other 90nm technologies from Intel, Texas Instruments and Sony/Toshiba have all used low-k at the critical metal levels. Consequently, the question is - can we classify this as a 90-nm part, or is it a shrunk 130nm device?"

UMC's publicity for their 90nm L90 process details the M1 pitch as 240nm, and the gate length as 70nm, and shows the IMD as FSG at the upper metal layers, with low-k (k~2.7) at the lower levels. Reported press indicates that UMC is planning to use Novellus' Coral carbon-doped oxide as their low-k material. So the part meets the published dimensions for 90nm, but not the structural details.

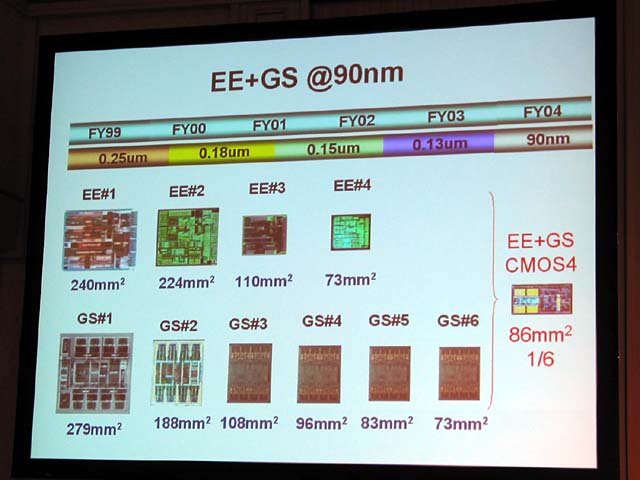

From Xilinx's perspective, UMC has presumably met the performance specifications for the XC3S200 - our sample is the standard speed product. The major advantage from 90-nm processing is the reduction in die size, and therefore cost - there are over twice as many die per wafer, compared with the equivalent product in 130nm technology.

The Spartan product is Xilinx' low-cost FPGA series, where the emphasis is on the performance/price ratio, targeted at the widest range of consumer applications. The nature of the IMD will not affect the die size, so as long as the device meets the performance requirements, it is not relevant - unless FSG/90-nm is cheaper than low-k/90-nm. It may in fact be cheaper, since FSG is a much more mature process.

Chipworks' findings for this device will be available in an upcoming structural analysis report, so that process engineers can examine this different approach to nanometer silicon. The report will also include an overview, package and die photos, process, transistor, materials and dielectric analysis, as well as critical die dimensions.