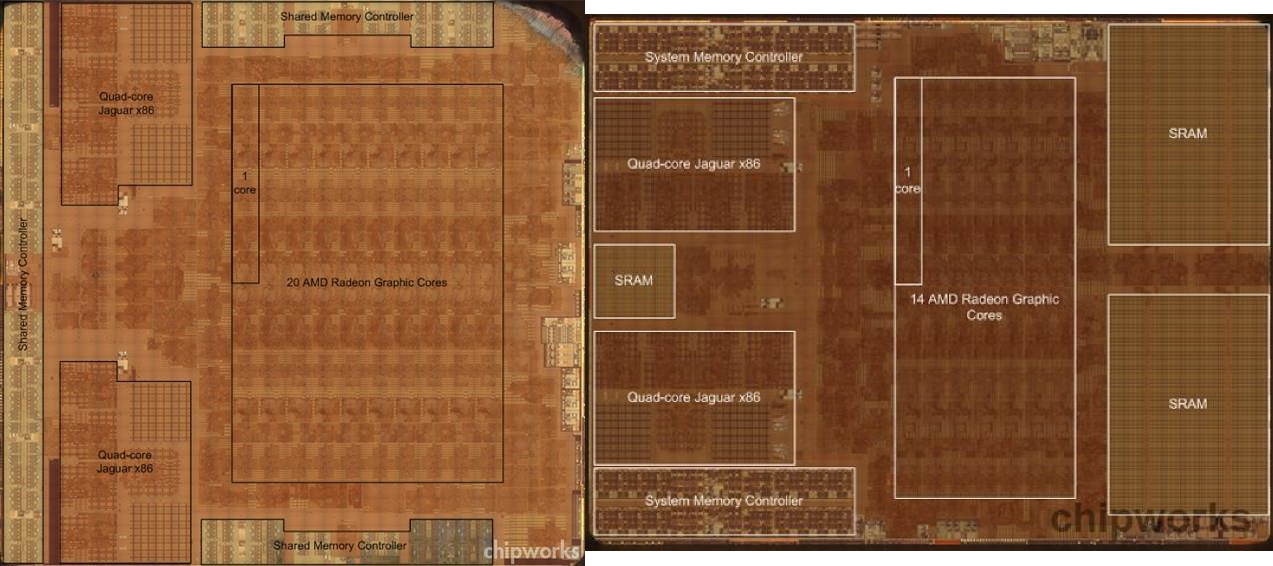

Looking at the Jaguar cores in each they look almost identical except for the extra bits in the corner of each Durango block. The same area for Orbis is blank.

What could that be? Would each CPU block have it's own audio core? Or would that be something else?

I'm not entirely convinced that it's not a matter of inconsistent box drawing.

The Orbis pic took the trouble to draw the line around the clock generator, while the Durango one drew through it.

Microsoft did state that it expanded the chip's on-die coherent interconnect, and those little blocks might be part of the customized interface.