You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

AMD: Zen 2 (Ryzen/Threadripper 3000?, Epyc 8000?) Speculation, Rumours and Discussion

Being "black out of love" I also "don't want to black".

That google translation is glorious.

Regards,

SB

That's racist.

Is pretty much impossible to understand unless we have a Chinese speaker here. Btw why we don't have any Chinese speakers here?

Same reasons less and less dev's post here, they dont want to put up with the various company fanboys?

Same reasons less and less dev's post here, they dont want to put up with the various company fanboys?

Last edited:

How do I know if my MoBo have it?It Just Works... as long as your motherboard vendor has it on QVL. Otherwise, good luck

How do I know if my MoBo have it?

Does it work? ;-)

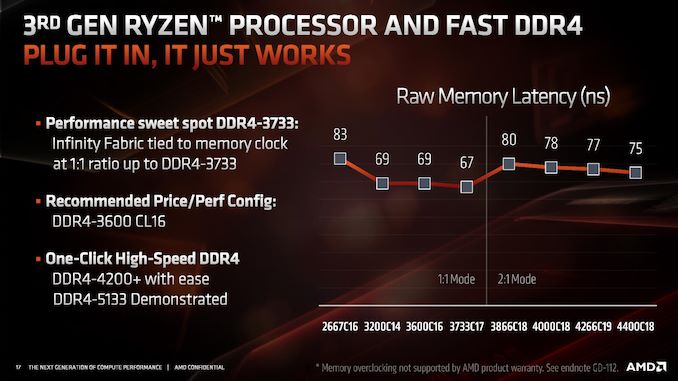

Me thinks dual chiplet CPUs (12/16 cores) will be more suitable for half-speed IF configs with high-speed RAM, where heavily multi-threaded workloads will be limited mostly by the BW than overall latency.Btw any thoughts on Zen's new memory latencies? I think its a reasonable compromise.

Check the memory QVL on your motherboard manufacturer's websiteHow do I know if my MoBo have it?

More importantly, does it work at advertised speeds and timings and is stable?Does it work? ;-)

Oh you mean Qualify Vendor List..yes my Mobo supports Ryzen. its a b350 strixx although asus haven't listed ryzen 3000 officially in the QVL page of the board.Check the memory QVL on your motherboard manufacturer's website

More importantly, does it work at advertised speeds and timings and is stable?

I'm referring to the high speed memory support, not the CPU support.Oh you mean Qualify Vendor List..yes my Mobo supports Ryzen. its a b350 strixx although asus haven't listed ryzen 3000 officially in the QVL page of the board.

Me thinks dual chiplet CPUs (12/16 cores) will be more suitable for half-speed IF configs with high-speed RAM, where heavily multi-threaded workloads will be limited mostly by the BW than overall latency.

The new IF links are 512 bit, 256 bits each way. This means the read bandwidth of the IF link matches the bandwidth of two DDR4 channels exactly. If you use DDR4 fast enough to force the IF links into 1:2 mode, you end up with a lot of DRAM bandwidth you can't use, unless you have perfect 50/50 read/write traffic (which you don't).

IE. The only use case of DDR4 faster than 3800MHz is for dual chiplet processors.

Cheers

hoom

Veteran

Been slowly digesting the Anandtech article, there's an awful lot of doubling of stuff there that should at least help out with a bunch of corner cases.

Bunch of other improvements also.

TAGE branch predictor could be a big win, from what I've been reading apparently is pretty bleeding edge tech, much better than Perceptrons they've been using previously (vid above says it was intended for Zen3 but they brought it forward ), though I did find a suggestion Intel has already been using this.

), though I did find a suggestion Intel has already been using this.

Regarding the AVX256: will they do double-rate 128bit?

Occurs to me this chiplet architecture is arguably a return to separate CPU-Northbridge-Southbridge

Bunch of other improvements also.

TAGE branch predictor could be a big win, from what I've been reading apparently is pretty bleeding edge tech, much better than Perceptrons they've been using previously (vid above says it was intended for Zen3 but they brought it forward

Regarding the AVX256: will they do double-rate 128bit?

Occurs to me this chiplet architecture is arguably a return to separate CPU-Northbridge-Southbridge

Rootax

Veteran

I wonder what impact avx256 will have on frequencies, temps, etc. On my (old) 5820k, using avx256 really push the temps vs non avx workload. And I my memory serves me right, they started avec different frequencies for avx256 / non avx256 with broadwell ? Or is it only with avx512/skylake-x ?

Similar threads

- Replies

- 220

- Views

- 92K

- Replies

- 2K

- Views

- 226K

- Locked

- Replies

- 4K

- Views

- 567K

- Locked

- Replies

- 835

- Views

- 192K

I hope the OC would be equal for non 570 MB. It would be disappointing if only 570MB could use the "new clock" OC

I hope the OC would be equal for non 570 MB. It would be disappointing if only 570MB could use the "new clock" OC