Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

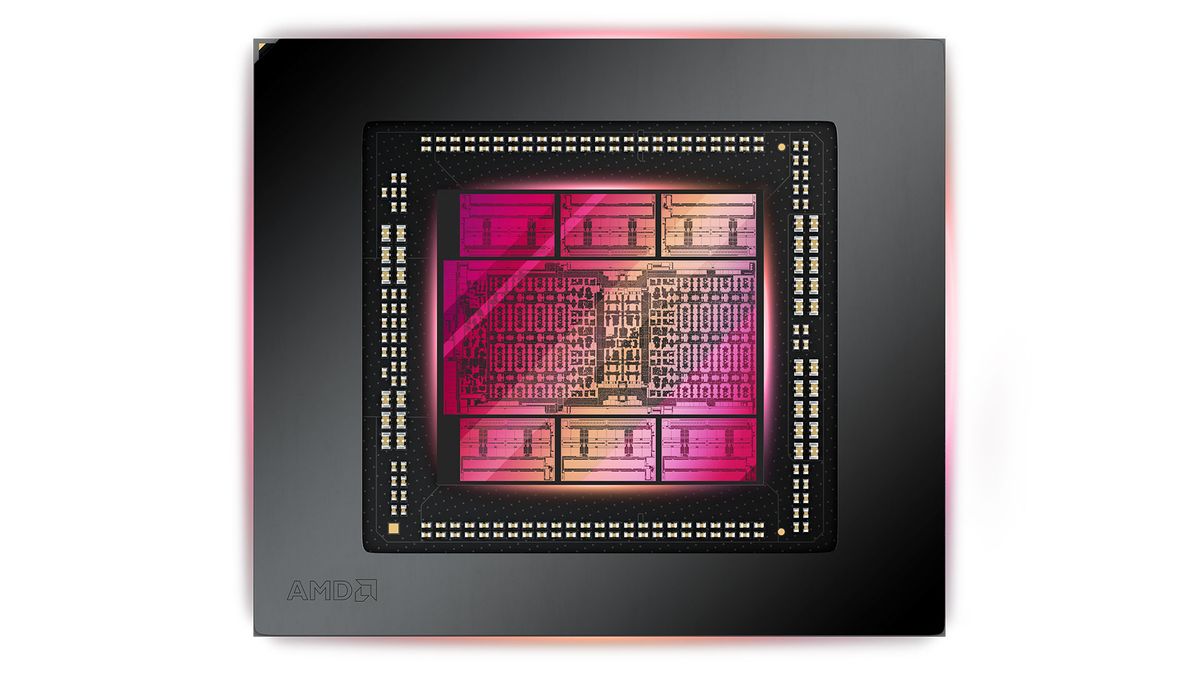

AMD Addresses Controversy: RDNA 3 Shader Pre-Fetching Works Fine

These aren't the bugs you're looking for.

DegustatoR

Legend

Should do the opposite of what we're seeing - make h/w simpler, reduce power consumption and allow it to clock higher.stupid question

at some point there was a rumor that amd will drop the HW scheduler for a software one

is that true? if so it maybe is at fault here?

There may be some negative effects on performance while the driver side compiler isn't tuned well for RDNA3 yet but it shouldn't be huge and it certainly shouldn't affect the clocks or anything.

Is there a purpose to spreading tweets from a self-proclaimed idiot?

Silent_Buddha

Legend

Is there a purpose to spreading tweets from a self-proclaimed idiot?

Maybe to help identify other idiots who aren't self-proclaimed?

Regards,

SB

Probably posted because of his earlier tweet, where he proclaimed something as a fact while it wasn't. Posting the follow up makes sure (as sure as you can anyway) the false information doesn't get to live on because not everyone follows that Twitter account?Is there a purpose to spreading tweets from a self-proclaimed idiot?

hurleybird

Newcomer

How much utilization is 3.6 GHz Navi 31 getting in Blender? How well does Navi 21 clock in Blender vs games and how much utilization does it get in comparison?

ofc, you wouldn't expect a casual 60% overclock to be stable even with low utilization, but these are questions I'd like to see the answer to if only as a bit of a sanity check.

ofc, you wouldn't expect a casual 60% overclock to be stable even with low utilization, but these are questions I'd like to see the answer to if only as a bit of a sanity check.

So it was all FUD. LOLAMD Addresses Controversy: RDNA 3 Shader Pre-Fetching Works Fine

These aren't the bugs you're looking for.www.tomshardware.com

Anyone have the press release PDF of RDNA 3?

Maybe. They're not going to acknowledge it, regardless, unless they break something fundamental to the functioning of the thing.So it was all FUD. LOL

"This is broken and we knew it before release" -> "This is an experimental feature not intended for this generation of product". (Though, the actual quote seems to outright deny that they broke something that was working in RDNA2.)

Unless we believe that they are slipping RDNA4 code into their public open source drivers before the release of RDNA3.

Bah!Maybe. They're not going to acknowledge it, regardless, unless they break something fundamental to the functioning of the thing.

"This is broken and we knew it before release" -> "This is an experimental feature not intended for this generation of product". (Though, the actual quote seems to outright deny that they broke something that was working in RDNA2.)

Unless we believe that they are slipping RDNA4 code into their public open source drivers before the release of RDNA3.

Who has the press deck pdf?

Last edited:

Bondrewd

Veteran

They actually did ship gfx12 commits in the open which was lmao.Unless we believe that they are slipping RDNA4 code into their public open source drivers before the release of RDNA3.

I do, what would you like from there?So it was all FUD. LOL

Anyone have the press release PDF of RDNA 3?

Edit: and for reference, implementing features not actually used is standard practice, latest great examples being Intels DLVR in Rocket Lake and AMDs TSVs in Zen 3 since the beginning (or was it already in Zen 2, can't remember for sure)

I was looking to read the entire PDF. Are you able to provide a link for it?I do, what would you like from there?

Edit: and for reference, implementing features not actually used is standard practice, latest great examples being Intels DLVR in Rocket Lake and AMDs TSVs in Zen 3 since the beginning (or was it already in Zen 2, can't remember for sure)

D

Deleted member 2197

Guest

Radeon RX 7000: AMD klärt Verwirrung um "Probleme" beim Shader-Prefetch

Nachdem Gerüchte aufgekommen sind, dass AMDs RDNA3-GPUs keinen Shader-Prefetch unterstützen, reagiert das Unternehmen mit einem Statement.

Tom's seems to have the full deck posted near end of this articleI was looking to read the entire PDF. Are you able to provide a link for it?

AMD RDNA 3 GPU Architecture Deep Dive: The Ryzen Moment for GPUs

Swimming with the next generation GPUs

stupid question

at some point there was a rumor that amd will drop the HW scheduler for a software one

is that true? if so it maybe is at fault here?

RDNA1 & 2:

4.5. Manually Inserted Wait States (NOPs)

Inserting S_NOP is not required to achieve correct operation.

RDNA3:

5.6. Data Dependency Resolution

Inserting S_NOP is not required to achieve correct operation.

5.7. ALU Instruction Software Scheduling

...This instruction(S_DELAY_ALU) is optional - it is not necessary for correct operation.

I would say it's still hardware scheduler, with software hints to power off some parts of scheduler.

Last edited:

Some good reads I found in the RDNA3 ISA document:

- 4.1.1. Cache Controls: SLC, GLC and DLC

- controls how load/store/atomic instructions interact with each cache level

- 5.2. Instruction Clauses

- talks about S_CLAUSE, followed by instructions on the same execution unit to be issued back-to-back without wave switching

- 5.7. ALU Instruction Software Scheduling

- talks about S_DELAY_ALU

- 7.6. Dual Issue VALU

- lists VOPD restrictions in detail

- 7.9. Wave Matrix Multiply Accumulate (WMMA)

- explains its matrix accelerator implementation

Similar threads

- Replies

- 85

- Views

- 11K

- Replies

- 179

- Views

- 15K

- Replies

- 67

- Views

- 13K

- Replies

- 15

- Views

- 2K