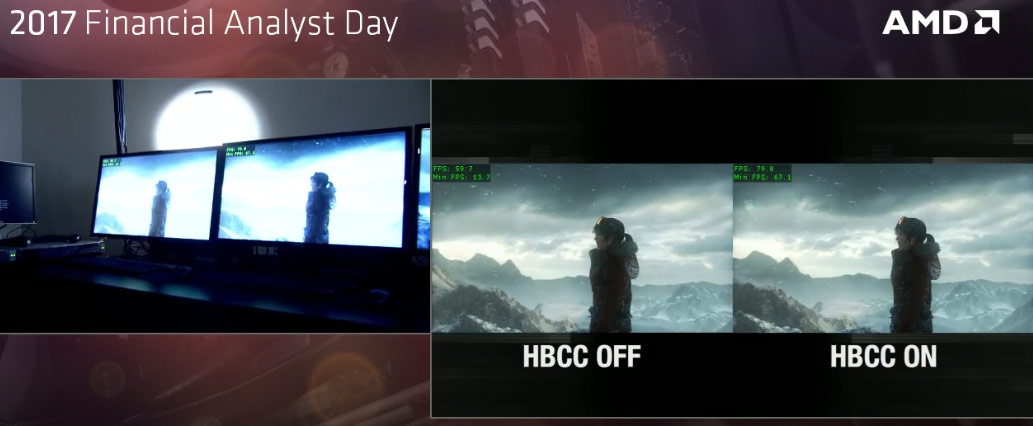

oh really ? And these tests have what connections to utilizing SSD in the memory pool ? https://www.techpowerup.com/231093/...e-controller-improves-minimum-and-average-fps

Which applies to the 8GB Vega cards. HBCC is in Radeon VII because it is in Vega 20. HBCC won't be too useful in a gaming card with 16GB of RAM, but it is useful in other configurations and uses for the chips. It could also be VERY useful for consoles, which have a relatively limited memory pool.