I have seen rumors or some BS about GDDR 6, but i have yet heard anything from Nvidia, ATI, or JEDEC,

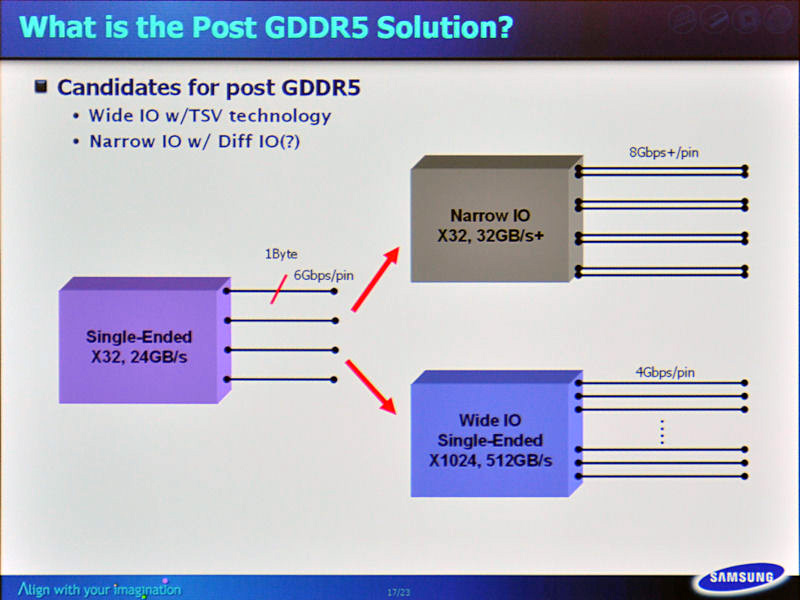

Since we dont want 512 bit memory lane ( because it is too expensive ), 256bit Memory will hit an wall sooner or later. Do we expect GDDR 5 to scale even further? Or We ditching GDDR5 for something else?

Since we dont want 512 bit memory lane ( because it is too expensive ), 256bit Memory will hit an wall sooner or later. Do we expect GDDR 5 to scale even further? Or We ditching GDDR5 for something else?