Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Next Generation Hardware Speculation with a Technical Spin [pre E3 2019]

- Thread starter AlNom

- Start date

-

- Tags

- 5 bytes non sequitur

- Status

- Not open for further replies.

anexanhume

Veteran

HBM would have several benefits over GDDR6, though I agree it’s hard to justify the price jump.But 410 GB/s is too low for next gen. They can use >500 GB/s cheap (compared to HBM2) GDDR6 chips for PS5. Why would they use a more expensive 410GB/s solution ?

1. Lower power

2. Smaller PSU

3. Less cooling

4. Smaller, simpler PCB (removal of memory bus is a chance to potentially reduce layers, remove laminations due to decreased interconnect density and speed, or use more cost effective dielectrics).

D

Deleted member 13524

Guest

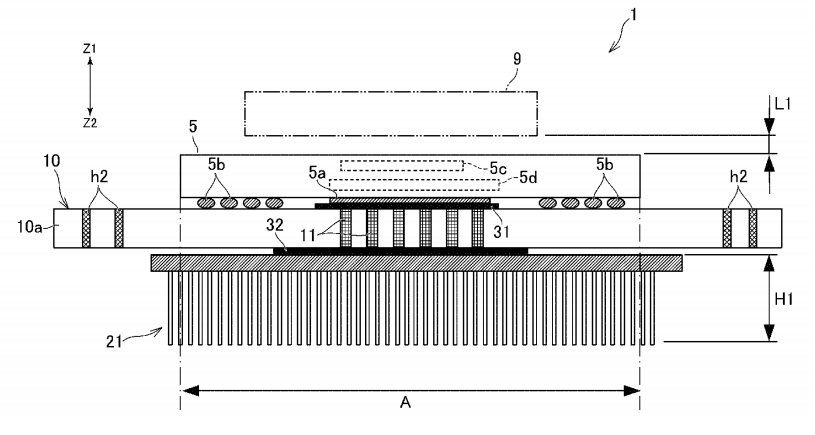

I wouldn't put aside the possibility of using 2 stacks of HBM directly under the SoC as we saw in that patent a while ago, the one with cross-pcb copper pipes for cooling the smaller chips.

anexanhume

Veteran

That pushes the density problem onto the chip package, which cannot do the density needed AFAIK. Unless they could embed interposer bridges?I wouldn't put aside the possibility of using 2 stacks of HBM directly under the SoC as we saw in that patent a while ago, the one with cross-pcb copper pipes for cooling the smaller chips.

D

Deleted member 13524

Guest

The purpose of the patent is to tackle that exact problem. A heatsink in the other side of the PCB would help cool the chips underneath.That pushes the density problem onto the chip package, which cannot do the density needed AFAIK. Unless they could embed interposer bridges?

anexanhume

Veteran

The patent covers cooling methodologies, not interconnect ones. Modern packages lack the density of interconnects to meet HBM needs, hence interposers on top of standard packages.The purpose of the patent is to tackle that exact problem. A heatsink in the other side of the PCB would help cool the chips underneath.

D

Deleted member 13524

Guest

Why would you need an interposer between HBM and a SoC if they're vertically stacked? HBM already uses TSVs. You'd just need to design the SoC to receive the connections through TSVs as well.The patent covers cooling methodologies, not interconnect ones. Modern packages lack the density of interconnects to meet HBM needs, hence interposers on top of standard packages.

When you guys are making these next-generation hardware price speculations - are you pricing exactly at cost ($399 worth of hardware) or pricing which is inclusive of losses (subsidize cost) that Microsoft or Sony would absorb?

a) $400 worth of hardware or at cost model (the magical $399 unicorn), no losses.

b) $500 worth of hardware for $399, Sony or Microsoft eats $100 in subsidize cost in the interim.

c) $600 worth of hardware for $399, Sony or Microsoft eats $200 in subsidize cost in the interim.

d) $600 worth of hardware for $499, Sony or Microsoft eats $100 in subsidize cost in the interim.

e) $700 worth of hardware for $499, Sony or Microsoft eats $200 in subsidize cost in the interim.

If Sony or Microsoft aren't going for 'El Cheapo' or the at cost model... I can see options 'b' and 'd' being highly probable. So the question becomes, what type of hardware and performance can we expect from options 'b' or 'd'?

Personally, I would love option 'd' if those are the choices between the two.

a) $400 worth of hardware or at cost model (the magical $399 unicorn), no losses.

b) $500 worth of hardware for $399, Sony or Microsoft eats $100 in subsidize cost in the interim.

c) $600 worth of hardware for $399, Sony or Microsoft eats $200 in subsidize cost in the interim.

d) $600 worth of hardware for $499, Sony or Microsoft eats $100 in subsidize cost in the interim.

e) $700 worth of hardware for $499, Sony or Microsoft eats $200 in subsidize cost in the interim.

If Sony or Microsoft aren't going for 'El Cheapo' or the at cost model... I can see options 'b' and 'd' being highly probable. So the question becomes, what type of hardware and performance can we expect from options 'b' or 'd'?

Personally, I would love option 'd' if those are the choices between the two.

Costs include a reference to either BOM or list price if you read through the thread. Without reference to list price and potential loss-leading, assume BOM costs.

Last edited:

Costs include a reference to either BOM or list price if you read through the thread. Without reference to list price and potential loss-leading, assume BOM costs.

Just wanted to make sure, I have seen threads/replies (not necessarily here) where members have added up $399 BOM pricing (nothing higher than $450 in BOM) worth of hardware, but never considered the possibilities that Sony or Microsoft would eat any BOM cost. Reasons being, that the current generation of systems weren't all that expensive to build, and Sony/Microsoft actually made a small amount ($25-$35) of profit off each unit. In other words, are we getting super price-conscious BOM hardware again, or something more reflective of BOM losses of PS2/XB-OG era?

Last edited:

With streaming on the horizon, I can’t see companies investing in loss leading for hardware. Loss leading is better invested for streaming services because as long as you are loading up users that hardware is being put to use. You don’t want to be loss leading and end up having your hardware be a dedicated UHD player or an exclusive machine.Just wanted to make sure, I have seen threads/replies (not necessarily here) where members have added up $399 BOM pricing (nothing higher than $450 in BOM) worth of hardware, but never considered the possibilities that Sony or Microsoft would eat any BOM cost. Reasons being, that the current generation of systems weren't all the expensive to build, and Sony/Microsoft actually made a small amount ($25-$35) of profit off each unit. In other words, are we getting super price-conscious BOM hardware again, or something more reflective of BOM losses of PS2/XB-OG era?

I largely suspect next gen will be priced close to BOM at the best.

cheapchips

Veteran

Are there any good numbers on loss leading hardware over time? I've an unsubstantiated feeling the costs came down pretty rapidly on everything except the original Xbox.

With streaming on the horizon, I can’t see companies investing in loss leading for hardware. Loss leading is better invested for streaming services because as long as you are loading up users that hardware is being put to use. You don’t want to be loss leading and end up having your hardware be a dedicated UHD player or an exclusive machine.

I largely suspect next gen will be priced close to BOM at the best.

I think long-term investments in game streaming services are good, however, it shouldn't supersede or impede greater investments into the current standalone hardware model either.

The problem these days is the frequency of density improvements. The cost of other parts is more predictable, but otherwise somewhat difficult to reduce in cost or have a strong dependency on the power consumption/thermal dissipation.Are there any good numbers on loss leading hardware over time? I've an unsubstantiated feeling the costs came down pretty rapidly on everything except the original Xbox.

Are there any good numbers on loss leading hardware over time? I've an unsubstantiated feeling the costs came down pretty rapidly on everything except the original Xbox.

PS2/XB360 were fairly costly to build, however, with good shrinks and parts becoming cheaper over time, PS2/XB360 started to make a reasonable profit during the 2nd or 3rd year of it's production.

anexanhume

Veteran

I'm not sure that HBM mounted on the bottom in a hole in the package is mechanically or thermally viable.Why would you need an interposer between HBM and a SoC if they're vertically stacked? HBM already uses TSVs. You'd just need to design the SoC to receive the connections through TSVs as well.

Wasn't there an odd heatsink/spreader/plate patent from Sony showing a design partially sandwiching in the motherboard? Possibly covering the SoC/APU and memory.

I could be thinking of something else...

I could be thinking of something else...

anexanhume

Veteran

Yes, that’s the patent to which we are referring. My original argument was that it was for PSVR 2 given the mention of EMI shielding and nearby antennas. I’m also skeptical such a method is suitable for a 100W+ TDP SoC.Wasn't there an odd heatsink/spreader/plate patent from Sony showing a design partially sandwiching in the motherboard? Possibly covering the SoC/APU and memory.

I could be thinking of something else...

Edit: patent in question:

http://www.freepatentsonline.com/WO2018216627A1.pdf

Last edited:

D

Deleted member 13524

Guest

What exactly do you think would be the tasks to be performed by this dedicated PSVR2 SoC, considering it would need such an exquisite cooling setup?My original argument was that it was for PSVR 2 given the mention of EMI shielding and nearby antennas.

I just can't see why a SoC would even be needed, much less one that would need a cooling setup that surpasses even those vapor chamber heatsinks we're seeing on gaming phones with a Snapdragon 855.

For a >100W SoC with HBM underneath, the smaller side-B heatsink would provide cooling for the memory while a more conventional and larger side-A heatsink (+ fan) would cool the SoC.I’m also skeptical such a method is suitable for a 100W+ TDP SoC.

The point for this would be to 3D-stack the HBM and SoC to forego the need for an interposer and its packaging costs, while at the same time preventing the memory stacks from overheating.

Why else would someone use this heatsink arrangement?

The main image seems more applicable to portable devices. But the text is very wide in application examples.

So it could be Portable PS4-lite, Vita 2, or a wireless VR.

Figure 4 shows how it can be designed to route traces around tetris-like holes for the heat sink. It looks expensive since it needs to be CNC'ed all over with high precision and very thin routing bits (which pcb manufacturers hate and charge extra because thin bits don't last long).

I still think cooling HBM from under is interesting. There's issues getting the traces around, but the HBM area doesn't have any connection to the PCB, only through the interposer. So that area doesn't seem very crowded. No external memory also means simpler ballout requirement. It needs power all around the SoC though.

Maybe an APU with no traces going through the center area, a square center with no balls would allow to poke a hole there (figure 6), and just have a bigger laminate to fit whatever ballout it needs. A large console wattage could use heatpipes connecting both sides.

A fanout interposer allows a lot of possibility to get the signals and power out of the way.

So it could be Portable PS4-lite, Vita 2, or a wireless VR.

Figure 4 shows how it can be designed to route traces around tetris-like holes for the heat sink. It looks expensive since it needs to be CNC'ed all over with high precision and very thin routing bits (which pcb manufacturers hate and charge extra because thin bits don't last long).

I still think cooling HBM from under is interesting. There's issues getting the traces around, but the HBM area doesn't have any connection to the PCB, only through the interposer. So that area doesn't seem very crowded. No external memory also means simpler ballout requirement. It needs power all around the SoC though.

Maybe an APU with no traces going through the center area, a square center with no balls would allow to poke a hole there (figure 6), and just have a bigger laminate to fit whatever ballout it needs. A large console wattage could use heatpipes connecting both sides.

A fanout interposer allows a lot of possibility to get the signals and power out of the way.

- Status

- Not open for further replies.

Similar threads

- Replies

- 85

- Views

- 17K

- Replies

- 21

- Views

- 4K

- Replies

- 25

- Views

- 3K

- Replies

- 22

- Views

- 9K