Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Intel ARC GPUs, Xe Architecture for dGPUs [2018-2022]

- Thread starter DavidGraham

- Start date

-

- Tags

- intel

- Status

- Not open for further replies.

VideoCardz leaked some stuff, haven't checked if it covers all the same as GN video, but VC watermarks their slides so at least GN isn't using themIs it safe to assume he was not under NDA but got the slides through other leaks/means? Or did someone else start the leak so once it's already public they can talk about it?

Bondrewd

Veteran

It's already inside of bunch of other shims like Proton so probably?My guess is FSR 1.0 will eventually be enabled through drivers

I guess.

D

Deleted member 13524

Guest

So could it run on a pair of Cadence Vision C5 matrix accelerators for a 720p output?XeSS is very much open sauce and runs everywhere with packed math.

The slides say 6 a.m. Pacific of August 19. Wasn't that >1h ago?So apparently GamersNexus decided it's ok to post a video filled with slides which show the NDA hasn't expired yet

D

Deleted member 2197

Guest

August 19, 2021

Bondrewd

Veteran

Ha!So could it run on a pair of Cadence Vision C5 matrix accelerators for a 720p output?

No, needs proper maff support.

But AMD will flay their WGP into a skinny ML acc only duty at a later date.

19m ago.Wasn't that >1h ago?

Oh, I misread it as pm, not amSo could it run on a pair of Cadence Vision C5 matrix accelerators for a 720p output?

The slides say 6 a.m. Pacific of August 19. Wasn't that >1h ago?

Intresting and impressive at the same time. Another competitor in the popular pc gpu market aint a bad thing.

DegustatoR

Legend

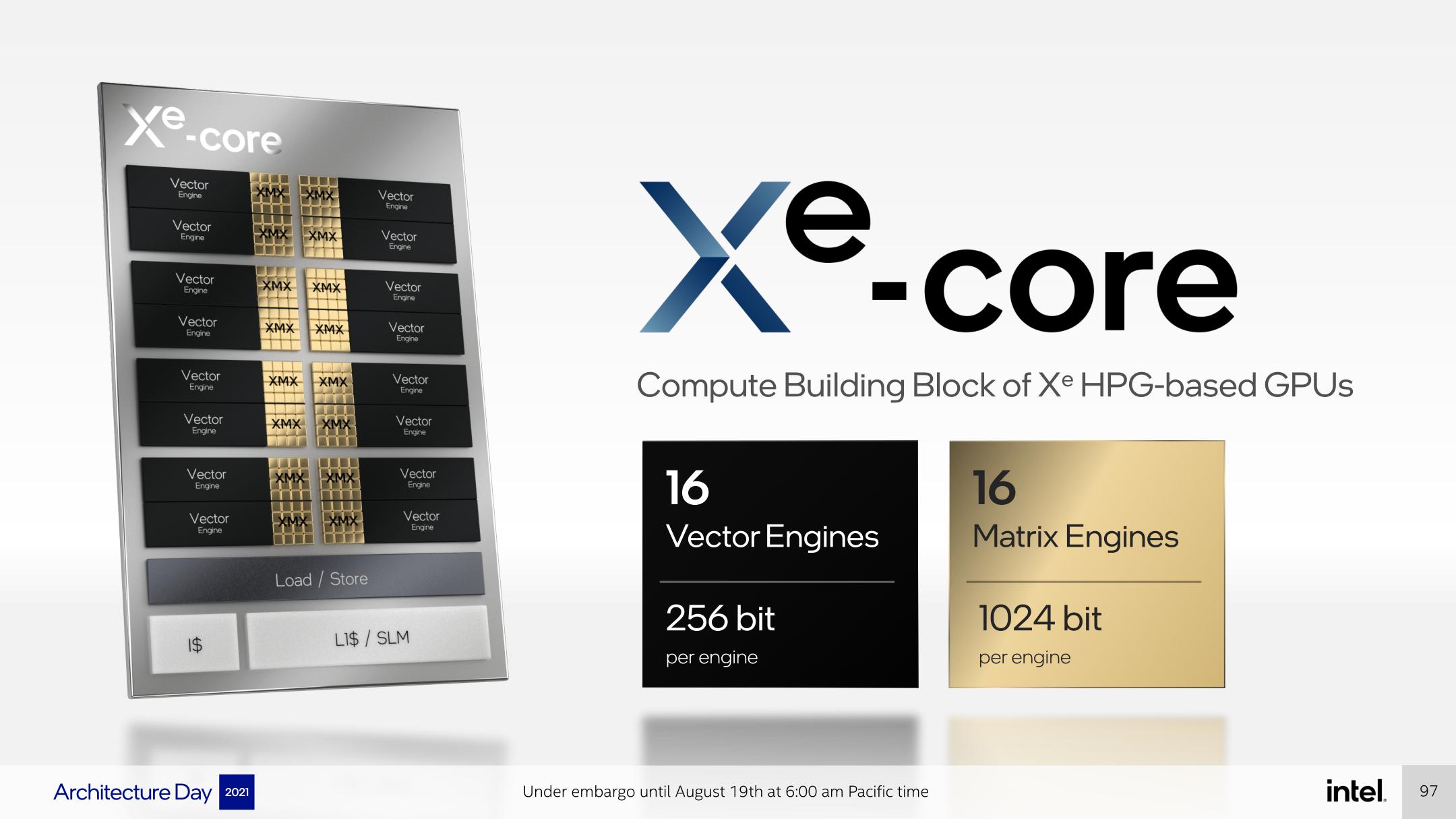

The pairing in the image is interesting.

Are they 8 wide or 16 wide in h/w?

In any case seems narrow for a modern GPU.

Bondrewd

Veteran

They're just 16EU subslices.Are they 8 wide or 16 wide in h/w?

I.e. 128ALU per Xe Core.

D

Deleted member 13524

Guest

So XeSS is confirmed to be cross-compatible with other GPUs, being able to run through DP4a, and it uses motion vectors like DLSS.

Great news.

Great news.

DegustatoR

Legend

https://www.anandtech.com/show/16895/a-sneak-peek-at-intels-xe-hpg-gpu-architectureMeanwhile, a 50% clockspeed uplift over Xe-LP would put Intel’s clockspeeds at roughly around 2GHz. That would be somewhere in between NVIDIA and AMD, who tend to have slightly lower and higher clockspeeds respectively. Or, to put things in terms of raw throughput, this would give a theoretical 8 slice Alchemist design 16.4 TFLOPS of single precision (FP32) shader/compute throughput, which would be almost 8x the rated throughput of the discrete Xe-LP DG1 video card.

Seems about what you'd expect from a 3070 level card.

Next year will certainly be interesting.

Great news for DLSS actually. Still dont know how Intel want to provide DP4a support without an API support.

Yes seems Intel's following in Nvidia's footsteps.

DegustatoR

Legend

If it's SYCL then it will run on OpenCL/CUDA/OneAPI/whatever AMD has.Still dont know how Intel want to provide DP4a support without an API support.

The vector unit has the same rate for FP32 and FP64 FMA op's, but double for FP16. Does that mean there is a separate FP64 pipeline alongside the FP32 one that probably serves the packed FP16?From GN

I bet that's what the cracks did. Or something along those lines.Sounds i could calculate one frame of PacMan every second to crack mining detection >

- Status

- Not open for further replies.

Similar threads

- Replies

- 498

- Views

- 78K

- Replies

- 211

- Views

- 8K

- Replies

- 3

- Views

- 1K