DegustatoR

Legend

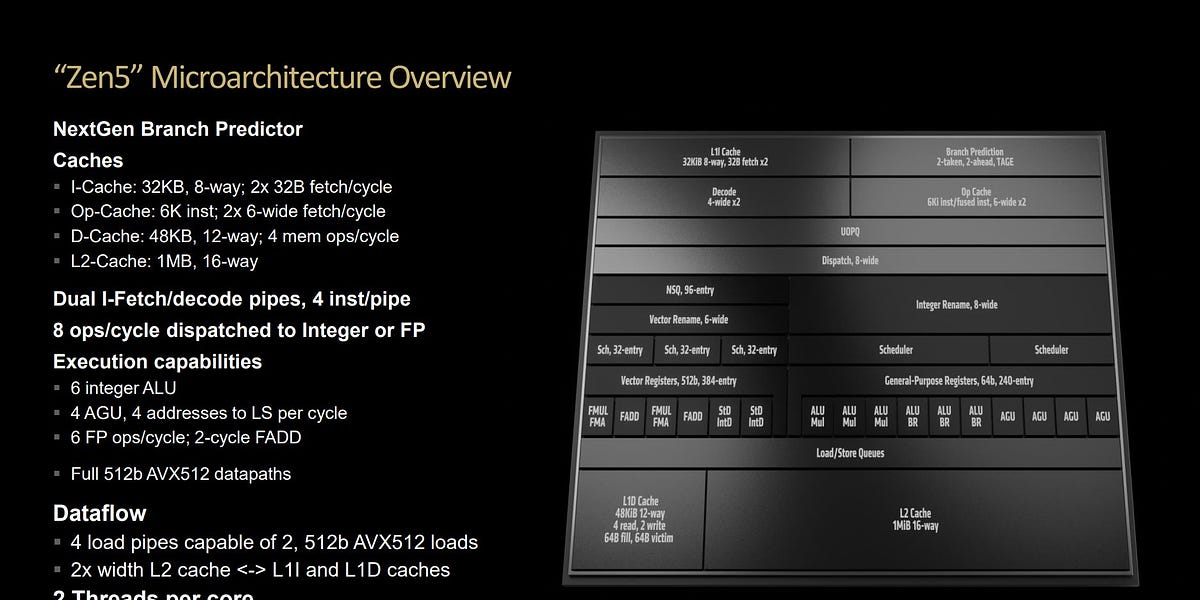

Ryzen AI have the old style 2-clock execution for AVX-512 which may in fact greatly affect it's perf/watt in a positive way. I dunno if it's a good idea to just call both of these "Zen 5".

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

I didn't mean to defend Ryzen 9700X, there's no reason to get it outside AVX512 use, just pointing out that this isn't Zen 5 introduction like claimed.We know that. Look at the headlines. This is about AMD execution which includes marketing.

Very Efficient Ryzen 7 9700X Held Back by Power Limits!

AMD 9700X and 9600X Benchmarks... OOF

AMD Ryzen 7 9700X Review - Zen 5 Sucks For Gaming!

Wasted Opportunity: AMD Ryzen 7 9700X CPU Review & Benchmarks vs. 7800X3D, 7700X, & More

AMD Ryzen 7 9700X review: YouTube hates this CPU

For the majority of potential customers, this will be their introduction to Zen 5. I know AMD marketing sucks but this is indefensible.

Lead Zen engineer "This launch isn't for gaming"We know that. Look at the headlines. This is about AMD execution which includes marketing.

Very Efficient Ryzen 7 9700X Held Back by Power Limits!

AMD 9700X and 9600X Benchmarks... OOF

AMD Ryzen 7 9700X Review - Zen 5 Sucks For Gaming!

Wasted Opportunity: AMD Ryzen 7 9700X CPU Review & Benchmarks vs. 7800X3D, 7700X, & More

AMD Ryzen 7 9700X review: YouTube hates this CPU

For the majority of potential customers, this will be their introduction to Zen 5. I know AMD marketing sucks but this is indefensible.

Disagree, AVX-512 is very niche (not in the least, because of Intel's abysmall adoption of their own instructions) . For non-worstation users, doubly so.Ryzen AI have the old style 2-clock execution for AVX-512 which may in fact greatly affect it's perf/watt in a positive way. I dunno if it's a good idea to just call both of these "Zen 5".

I don't blame this on reviewers. We had Ryzen 1700X, Ryzen 2700X, Ryzen 3700X, Ryzen 5700X, and Ryzen 7700X which were most definitely used for gaming. To release a 9700X and say it's not for gaming is silly.Lead Zen engineer "This launch isn't for gaming"

Reviewers "Bitching about no gaming performance"

I mean, yes it's a failure on AMD to control the press. But how many sales does seeding review samples to drama factories like these actually get them? It's a relevant question all IHVs should be asking.

I'm balking at the suggestion that Zen 5 is not for gaming. When Intel introduced AVX512 on the desktop nobody said "oh well these must not be for gaming".Pretty sure that means Zen 5 rather than specific SKU, as in, they focused on other things in this architecture. AVX512 should be a telltale sign for everyone on that, it's pretty nonexistant on consumer space and Intel killed it off in their consumer CPUs already.

Also DIY space is more than gaming.

The 7700X also shows gains from disabling SMT. Is this expected behavior?Yeah, they pretty clearly and obviously call out the 9600x, 9700x, and the as-yet-unreleased 9900x along side their "Gaming Leadership". Seems like they're intended for gaming, at least partially...

The TPU article about disabling SMT is a curious result. I wonder if this lends any credence to the memory subsystem being unable to feed such a wide beast, and maybe this suggests more cache (eg the 3D VCache parts) will enjoy the "full" potential of the chip? Will be interesting to see.

You must understand the difference between "not developed gaming first" and "you definitely aren't allowed to game on these ever" (exaggerated to make the point). It isn't you can't game or games don't work faster(/watt X3D aside), it's that the architecture evolutions were designed for other workloads, whatever gains gaming got weren't the priority and probably mostly comes from the optimizations made for other types of loads. Thus gaming workloads get smaller improvements this gen than some other areas, like that AVX512.I'm balking at the suggestion that Zen 5 is not for gaming. When Intel introduced AVX512 on the desktop nobody said "oh well these must not be for gaming".

Notice that these slides include the entire Zen 5 product stack.

That may have been the focus of the architecture, but that's not something that was effectively communicated by AMD's marketing before launch.You must understand the difference between "not developed gaming first" and "you definitely aren't allowed to game on these ever" (exaggerated to make the point). It isn't you can't game or games don't work faster(/watt X3D aside), it's that the architecture evolutions were designed for other workloads, whatever gains gaming got weren't the priority and probably mostly comes from the optimizations made for other types of loads. Thus gaming workloads get smaller improvements this gen than some other areas, like that AVX512.

This we can agree on.That may have been the focus of the architecture, but that's not something that was effectively communicated by AMD's marketing before launch.