In that case, would there be any benefit to including a heatsink on the underside of a PCB without passing through it too? So it needn't interfere with the HBM data paths, but could still cool the lower layers?

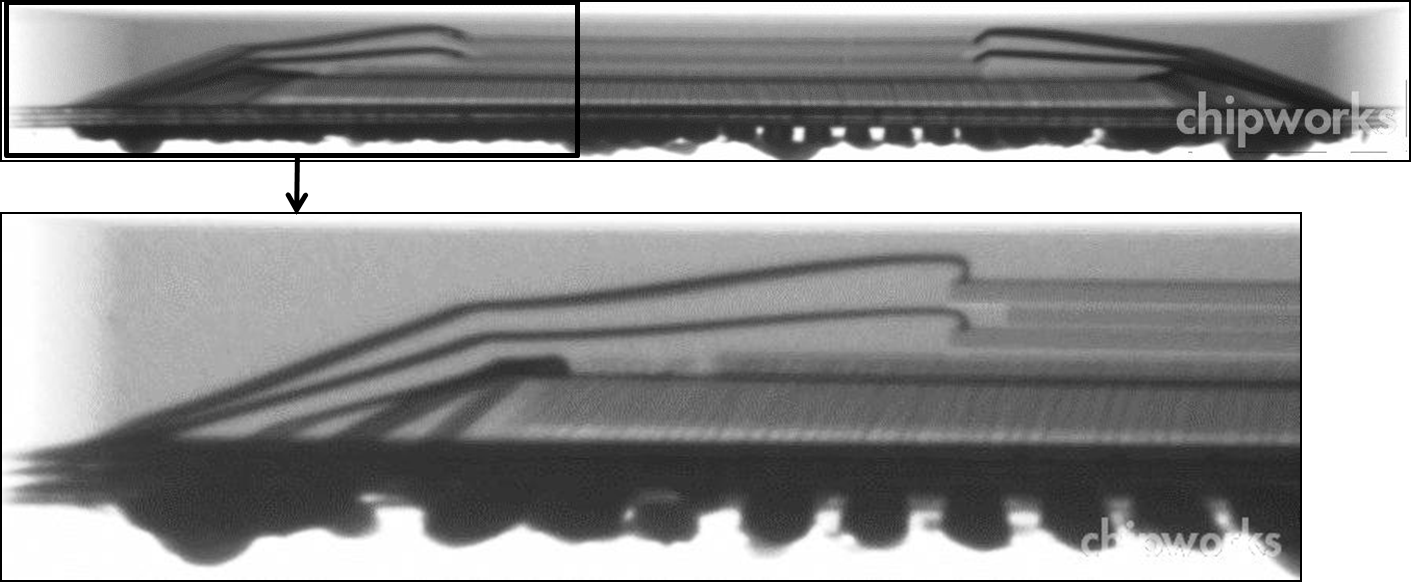

That places many layers of material between the active silicon and the heatsink. I am not sure if you meant PCB as in the motherboard, that's several layers of insulation, then the layer of solder balls for the chip package, then multiple layers of the package, then the interposer, then the base area of the stack.

There is some heat transfer capacity for a chip through its traces into the motherboard, for a limited amount of dissipation. That tends to track with limited power consumption and a sufficient ratio of connected traces in the PCB.

HBM's distance from the board is greater, and more of its smaller connections provide don't go very far since they're in the interposer and go straight to the SOC.

If you meant getting the heatsink up to the base of the chip package or up to the base of the interposer, it might be closer. Wires need to be routed around it, pad area between each layer needs to be sacrificed, and the mechanical properties shift. The amount of transport and how well it would turn out in models or implementation is outside of my sphere of expertise.

Or maybe feed a thermally conductive top layer with both the main, top heatsink, and cascade thermally conductive wires down the sides of the HBM stack to the bottom heatsink too?

The small cross section of the wires and distance traveled seem like they would limit the dissipation through the wires. The underside heatsink patent put much more metal through the PCB and package to the chip in order to provide a lower thermal resistance path.