D

Deleted member 13524

Guest

I'm saying this news isn't very useful to us. Having a code that deciphers to 'unknown' isn't all that informative.

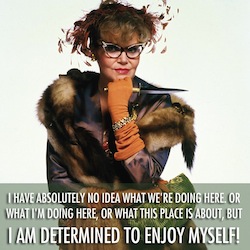

Chris1515 posts exciting code. What does it mean?? A cheetsheet, and decoding, and...a lot of unknowns, but we can safely say AMD have an 8 core CPU. Revelation!! So much Excitement! (sarcasm).

It's the first time we're seeing a Zen + Navi codename (last week another codename suggested that 7nm APU Renoir will have a Vega GFX9 GPU), and as @Kaotik mentioned it carries the same 2nd character as the other semi-custom SoCs for gaming consoles.

It says the base clock is 1.6GHz which is a really strong indicator for backwards compatibility for the PS5, and the 8 cores at 3.2GHz tells us a lot on what to expect for CPU performance.

Apart from Phil Spencer making an appearance at AMD's CES presentation to confirm they're working together on the XBox 4, this is probably the biggest palpable news we've had about the next gens, so.. I don't get your unenthusiasm either.