version said:"Oh...I forgot about that! ...So is that 1 TOPS of 8bit Integers, peak, fully pipelined!"

no, not multiply-add instruction, hence only 500 GOPS

+PPE altivec with 64 GOPS

but parallel with permute 1 TOPS

Marketing will like this!

version said:"Oh...I forgot about that! ...So is that 1 TOPS of 8bit Integers, peak, fully pipelined!"

no, not multiply-add instruction, hence only 500 GOPS

+PPE altivec with 64 GOPS

but parallel with permute 1 TOPS

version said:"Well not really, But altiVec can operate across an array of 16 bytes..."

hmm, altivec compute with 8*halfword(16 bit) too ??

no, not multiply-add instruction, hence only 500 GOPS Smile

+PPE altivec with 64 GOPS

but parallel with permute 1 TOP

archie4oz said:version said:"Well not really, But altiVec can operate across an array of 16 bytes..."

hmm, altivec compute with 8*halfword(16 bit) too ??

Yes...

no, not multiply-add instruction, hence only 500 GOPS Smile

+PPE altivec with 64 GOPS

but parallel with permute 1 TOP

If you had the same dispatch and execution layout as the 745x/744x CPUs then you could process 2 vector integer ALU ops per clock...

Why would this be pushing it?Jaws said:But three beefed up PPE cores would be pushing it at 90nm and we may only see two.

Doesn't Every integer SIMD?Archie said:Well not really, But altiVec can operate across an array of 16 bytes...

That only works if the core can dual issue FP and VMX instructions together (There's a reason why PSP primary cpu is only rated at 2.6GFlops rather then 3.3 even though the total number of FMACs would give you the latter number).Akira said:Actually according to Aaron Spink (a real engineer) a better estimate is 105 GFLOPS, taking into account the main FPUs on the PPC cores as well as the FP SIMD units

Absolutely if we beleive that Cell is possible for PS3, there is absolutely no reason to suggest that XeCPU won't be. If we assume that the Xe enhanced VMX takes 50% more die space per core, its still not that big compared to Cell.Fafalada said:Why would this be pushing it?

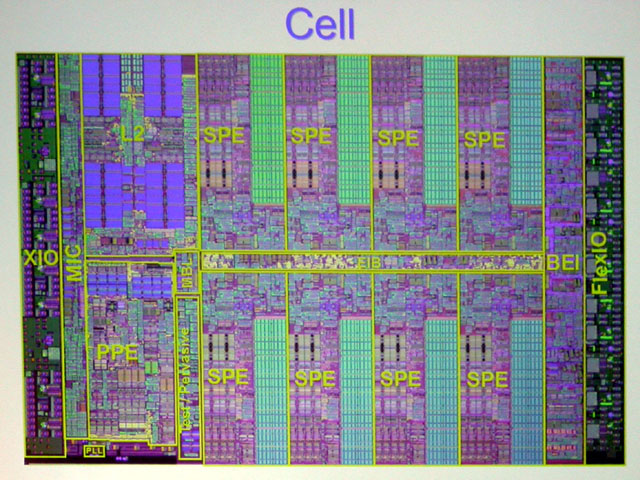

Eyeballing it from the Cell die, 3 PPEs(but slightly larger) with 1MB L2 wouldn't be much larger then one half of the 8/1 Cell size... and also targetting lower Mhz.

Say we give it ~160mm2, is that really so unreasonable?

Now... should there be some other changes... (such as say, 2MB of L2) then I would start wondering about the size of the chip...

FPU and VMX are independent IIRC.Fafalada said:That only works if the core can dual issue FP and VMX instructions together (There's a reason why PSP primary cpu is only rated at 2.6GFlops rather then 3.3 even though the total number of FMACs would give you the latter number).

So... calling any Xenon insiders... can it

DeanoC said:Absolutely if we beleive that Cell is possible for PS3, there is absolutely no reason to suggest that XeCPU won't be. If we assume that the Xe enhanced VMX takes 50% more die space per core, its still not that big compared to Cell.Fafalada said:Why would this be pushing it?

Eyeballing it from the Cell die, 3 PPEs(but slightly larger) with 1MB L2 wouldn't be much larger then one half of the 8/1 Cell size... and also targetting lower Mhz.

Say we give it ~160mm2, is that really so unreasonable?

Now... should there be some other changes... (such as say, 2MB of L2) then I would start wondering about the size of the chip...

FPU and VMX are independent IIRC.Fafalada said:That only works if the core can dual issue FP and VMX instructions together (There's a reason why PSP primary cpu is only rated at 2.6GFlops rather then 3.3 even though the total number of FMACs would give you the latter number).

So... calling any Xenon insiders... can it

OT Whats this about PSP and 222Mhz not 333Mhz?

Well I assumed that much - but FPU and VFPU are also independant but that doesn't mean you can co-issue themDeanoC said:FPU and VMX are independent IIRC.

Fafalada said:Why would this be pushing it?Jaws said:But three beefed up PPE cores would be pushing it at 90nm and we may only see two.

Eyeballing it from the Cell die, 3 PPEs(but slightly larger) with 1MB L2 wouldn't be much larger then one half of the 8/1 Cell size... and also targetting lower Mhz.

Say we give it ~160mm2, is that really so unreasonable?

Now... should there be some other changes... (such as say, 2MB of L2) then I would start wondering about the size of the chip...

...

Fafalada said:Why would this be pushing it?Jaws said:But three beefed up PPE cores would be pushing it at 90nm and we may only see two.

Eyeballing it from the Cell die, 3 PPEs(but slightly larger) with 1MB L2 wouldn't be much larger then one half of the 8/1 Cell size... and also targetting lower Mhz.

Say we give it ~160mm2, is that really so unreasonable?

Now... should there be some other changes... (such as say, 2MB of L2) then I would start wondering about the size of the chip...

Why indiivudal caches though? L2 locking is already there(that's how GPU reads out from it in the first place) and once you locked it, isn't it easier to allocate the chunks for each core by software? So you even get to decide how much "local memory" each "streaming processor" will get.They could use an individual L2 cache for each core. This way they could create the capability to lock a chunk of the L2, in effect creating something similar to a SPU's local storage (but virtually addressed) and gain the capabilities of a streaming processor without the SPU drawbacks.

Fafalada said:Why indiivudal caches though? L2 locking is already there(that's how GPU reads out from it in the first place) and once you locked it, isn't it easier to allocate the chunks for each core by software? So you even get to decide how much "local memory" each "streaming processor" will get.They could use an individual L2 cache for each core. This way they could create the capability to lock a chunk of the L2, in effect creating something similar to a SPU's local storage (but virtually addressed) and gain the capabilities of a streaming processor without the SPU drawbacks.

Akira said:Actually according to Aaron Spink (a real engineer)

I tend to agree, but not sure how 'beefy' it is... As I wrote in some other thread Cell has the hardware virtualization feature which MS won't need for Xenon while the assembler for VC8 seems to be able to interpret instructions for the Vanderpool Technology from Intel in addition to the Xbox 2 PPC opcodes. It's nice to run 2 OSs simultaneously on a desktop PC media center, but it's too much for Xenon.Megadrive1988 said:I for one do not believe Xenon CPU cores are based on Cell's PU/PPE. I think Xenon's cores are probably beefier Power/POWER cores than the PU/PPE in Cell.

I also imagine the hardware logic requirement to implement individual caches would be somewhat higher then one unified one? But anyway, I think it's just nicer if I could sliceup the locked portion any way I see fit rather then have a predetermined setup.Gubbi said:You might be right that having a single large L2 cache with locking is easier. It certainly makes scheduling easier, otherwise you'd want the OS to schedule threads that access the locked region on the core that has locked the memory.

Well it just makes more sense to me, GPU generally wants to do batch memory transfers, not read/write single cache lines, and in cases where CPU and GPU cooperate on processing same data like this, I will most likely do some kind of streaming setup on CPU, so I would want to lock cache for that purpose also.BTW. Why would you need to lock part of the L2 to have the GPU read from it? The caches are kept coherent with the rest of the memory system so a memory request would be served by the L2 if data was found in it.

Jaws said:I'm expecting Xe CPU sub 200 mm2 from MS talk of being more profitable with Xenon and prior precedent with Xbox CPU die size but who knows, they can push 4 cores and clock lower. If they used two cores instead, I'd expect them to clock them 4 Ghz +...

Jaws said:I think your missing my point of a smaller die and clocking higher, e.g. assuming identical cores,

3 cores @ 3GHz = 2 cores @ 4.5 GHz for FLOPS

Just an analogy but the higher clocked die should give better single threaded performance. They could go with 2-4 cores depending on clock, heat, die size and performance for single/multi-threading. They already have a very capable R500 for multi-threading performance so may decide to boost single threaded performance on the CPU. A smaller die CPU should give better yields/cost also.

a688 said:Jaws said:I think your missing my point of a smaller die and clocking higher, e.g. assuming identical cores,

3 cores @ 3GHz = 2 cores @ 4.5 GHz for FLOPS

Just an analogy but the higher clocked die should give better single threaded performance. They could go with 2-4 cores depending on clock, heat, die size and performance for single/multi-threading. They already have a very capable R500 for multi-threading performance so may decide to boost single threaded performance on the CPU. A smaller die CPU should give better yields/cost also.

A faster clocked die doesn't have to have better performance at all. Look at the Pentium M compared to the Pentium 4. What you need to look at is IPC * speed, not just speed.