Install the app

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

NVIDIA Tegra Architecture

- Thread starter french toast

- Start date

-

- Tags

- nvidia

A1xLLcqAgt0qc2RyMz0y

Veteran

All the jokes aside from the elaborate RHY hoax, is there any confirmed accounts of TK1's die size? I'm surprised it isn't easily attainable given TK1 has been out for over a month now (with Jetson).

Yes, I wonder why no one just pops the lid off the K1 on the Jetson and takes a high res picture. Its only $192. You would think some technical publication would be able to swing a $192 purchase.

https://developer.nvidia.com/jetson-tk1

Yes, I wonder why no one just pops the lid off the K1 on the Jetson and takes a high res picture. Its only $192. You would think some technical publication would be able to swing a $192 purchase.

https://developer.nvidia.com/jetson-tk1

Package size isn't die size, it's just a lower limit. The die can and often is a lot smaller than the package.

To find die size you need to burn through the package first which is a lot more expensive.

The memory is off-package for K1, which helps. Die size is 121mmsq.

Isn't that extremely large for a mobile SoC? Or have they grown in recent years?

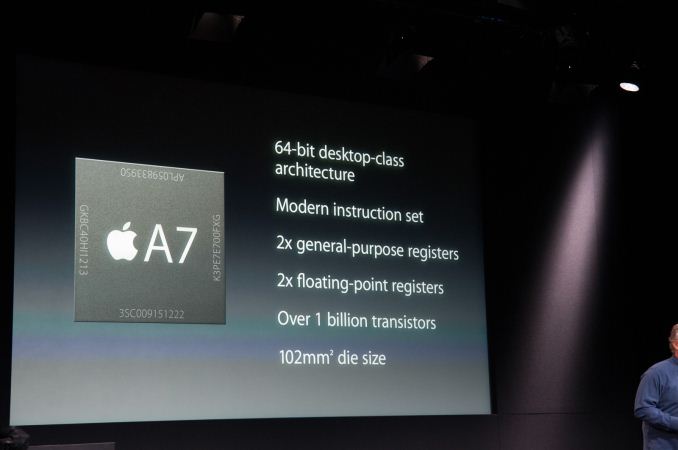

Apple's A7 is 102mm2.Isn't that extremely large for a mobile SoC? Or have they grown in recent years?

D

Deleted member 13524

Guest

The A6X is 120mm^2 and the A5X is over 160mm^2.

The A7 didn't get a "tablet version" with a 4-channel memory controller because of LPDDR3, but I wouldn't be surprised if we see an A8X this year.

The A7 didn't get a "tablet version" with a 4-channel memory controller because of LPDDR3, but I wouldn't be surprised if we see an A8X this year.

Ah, so mobile SoCs have indeed grown in recent years. Thanks.

While I don't recall exact figures I think the majority of Samsung's own Exynos SoCs should also exceed the 100mm2 mark. In the given case with K1 we should note that perf/mm2 is quite high.

On a sidenote manufacturing costs per SoC and size are also subject to volumes IMO. When you're Apple or QCOM and you're dealing with N millions of SoC volumes, manufacturing costs should be a quite a bit lower than in other cases. It shouldn't mean that Apple didn't "feel" the 165mm2 of the A5X for instance, but it definitely felt it way less than some other SoC manufacturer that would design such a big SoC and sell it only at a fraction of the quantity Apple is selling.

Nebuchadnezzar

Legend

The 5422 is about 136.6mm2.

The 5422 is about 136.6mm2.

Which might sound OT, but brings me to the point of perf/mm2 again. Even if Samsung would use the newer T760 Mali GPU IP the perf/mm2 ratio especially for the GPU is a complete joke to what GK20A is doing in K1

Which might sound OT, but brings me to the point of perf/mm2 again. Even if Samsung would use the newer T760 Mali GPU IP the perf/mm2 ratio especially for the GPU is a complete joke to what GK20A is doing in K1

Isn't that kinda of a pointless point since nVIDIA will not compete on the mainstream mobile phone/tablet market anymore? Whatever the T760 Mali GPU offers is good enough for the market it targets, while GK20A is just overkill on the same market. Which ultimately was a result of terribly bad judgement and planning by nVIDIA when developing Tegra, IMO.

EDIT - Your post is not OT at all, this is the Tegra Roadmap thread

Last edited by a moderator:

Isn't that kinda of a pointless point since nVIDIA will not compete on the mainstream mobile phone/tablet market anymore? Whatever the T760 Mali GPU offers is good enough for the market it targets, while GK20A is just overkill on the same market.

GK20A is arguably overkill for how the ULP SoC market has shaped up in terms of featureset; T760 and any other GPU IP therefore is typically highly scalable. You can scale on a T760 theoretically up to 16 clusters if needed. In the above 5422 case example you have a 136mm2 SoC monster, for which TegraK1 is by a bit smaller but if you clock the GPU even at just 150MHz it'll run circles around the first.

If you should mean DX11 for instance I can't blame them either; IMG's marketing was shouting from all rooftops that Rogue will bounce from DX10 to DX11.x, ARM also mentioned somewhere stuff about tessellation in its T7xx material (albeit the word behind the curtain is that it's far from being DX11), Vivante made similar announcements and while Qualcomm had been hammered in a relative sense for being supposedly late with a DX11 GPU they're amongst the first to deliver them after all.Which ultimately was a result of terribly bad judgement and planning by nVIDIA when developing Tegra, IMO.

In that regard I'm more puzzled about why QCOM chased its heels to get DX11 into its Adreno4x0 family of GPUs than anything else; NV to its defense had Kepler already developed and it's sounds like less work to try to shrink an existing design then start from a tabula rasa with a somewhat ~DX10 full compute capable design.

WTF do I need tessellation for in the next GalaxyS5 exactly? Unless someone has the superdumb idea to create a live wallpaper for Android with a shitload of tessellation in order to empty the phone's battery in a blink of an eye, I don't see it being of any meaningful use there.

If you should mean DX11 for instance I can't blame them either; IMG's marketing was shouting from all rooftops that Rogue will bounce from DX10 to DX11.x, ARM also mentioned somewhere stuff about tessellation in its T7xx material (albeit the word behind the curtain is that it's far from being DX11), Vivante made similar announcements and while Qualcomm had been hammered in a relative sense for being supposedly late with a DX11 GPU they're amongst the first to deliver them after all.

I'm not necessarily speaking about feature set, as much as market segmentation. Just as they have piss poor GPU SKU's, they should have planned for less overpowered SoC as well. This way, as the overkill SoC did not gain track, they could at least manage to keep a presence on the market.

I'm not necessarily speaking about feature set, as much as market segmentation. Just as they have piss poor GPU SKU's, they should have planned for less overpowered SoC as well. This way, as the overkill SoC did not gain track, they could at least manage to keep a presence on the market.

Α DX11 tessellation unit isn't exactly irrelevant even indirectly to power consumption as it consumes more die area than many would imagine, plus of course all the other requirements.

From what I had heard Imagination had skipped improved rounding in present Rogue GPUs which accounted for a healthy die area difference in ALUs, which bounced them from DX10.1 to DX10.0. That alone given I wouldn't want to imagine what all the additional requirements for DX11 would cost in hw. I might be wrong but I wouldn't be surprised if it would be in the =/>50% region.

Take that hypothetical figure and consider a SoC GPU block that's 20mm2 and another that's 30mm2 under the same process and frequency target and tell me what power could look like for the first vs. the latter.

Α DX11 tessellation unit isn't exactly irrelevant even indirectly to power consumption as it consumes more die area than many would imagine, plus of course all the other requirements.

From what I had heard Imagination had skipped improved rounding in present Rogue GPUs which accounted for a healthy die area difference in ALUs, which bounced them from DX10.1 to DX10.0. That alone given I wouldn't want to imagine what all the additional requirements for DX11 would cost in hw. I might be wrong but I wouldn't be surprised if it would be in the =/>50% region.

Take that hypothetical figure and consider a SoC GPU block that's 20mm2 and another that's 30mm2 under the same process and frequency target and tell me what power could look like for the first vs. the latter.

I understand that, but like you said Tessellation in a phone is pointless. nVIDIA followed the trend mindlessly. It could have been a more sensible strategy to have a good enough SoC, without all the bells and whistles of DX11 for the mainstream 200 euros market, along with the TK1 powerhouse for other segments. I guess Tegra4i was supposed to be that, but it came too late. They aimed for the jugular in a market they had fearful competitors in and barely any experience at. Wrong strategy in this case, IMO.

Nebuchadnezzar

Legend

Samsung puts IP blocks on their SoCs most of you never heard of, I don't think discussing GPU perf/mm2 is fair when you don't even know how much the GPU takes up from those 136mm2. My guess it's less much less than a third.

D

Deleted member 13524

Guest

GK20A is arguably overkill for how the ULP SoC market has shaped up in terms of featureset; T760 and any other GPU IP therefore is typically highly scalable. You can scale on a T760 theoretically up to 16 clusters if needed. In the above 5422 case example you have a 136mm2 SoC monster, for which TegraK1 is by a bit smaller but if you clock the GPU even at just 150MHz it'll run circles around the first.

Wut?

1080p Manhattan:

TK1: 28.1 FPS

Exynos 5422: 8.6 FPS

Assuming 650MHz for that TK1 and a linear scaling with clocks, performance at 150MHz would be (150*28.1)/650 = ~6.5 FPS.

This doesn't look like running circles..

Sure, Samsung's SoC division hasn't been terribly successful ever since they lost access to Intrinsity's services, but I think you're being a bit too melodramatic.

In that regard I'm more puzzled about why QCOM chased its heels to get DX11 into its Adreno4x0 family of GPUs than anything else; NV to its defense had Kepler already developed and it's sounds like less work to try to shrink an existing design then start from a tabula rasa with a somewhat ~DX10 full compute capable design.

WTF do I need tessellation for in the next GalaxyS5 exactly? Unless someone has the superdumb idea to create a live wallpaper for Android with a shitload of tessellation in order to empty the phone's battery in a blink of an eye, I don't see it being of any meaningful use there.

Whatever made you believe that tesselation is a power hog by itself, is probably wrong.

If the final visual result is the same and both target the same framerate, a model with lots of geometry will probably consume more power than the same model with less geometry+tesselation.

Tesselation can - and should - be used as a power/performance saving feature in mobile devices.

Qualcomm's (and all others') pursuit for full DX11 compliance are probably related to Microsoft's plans for Windows 9.

Similar threads

- Locked

- Replies

- 10

- Views

- 1K

- Replies

- 0

- Views

- 648

- Replies

- 11

- Views

- 3K

- Replies

- 90

- Views

- 17K

- Replies

- 21

- Views

- 10K