http://techon.nikkeibp.co.jp/article/NEWS/20051005/109392/?ST=lsi (requires free reg)

Nikkei Tech-on has an article about the exibition by NEC Electronics at PROTEC JAPAN 2005 which was held along with CEATEC JAPAN 2005 at the same venue from Oct. 5. The short article features Xenos.

Though 22.4GB/s looks enough already, is there any impact of this downspec on game development? Another possible theory is it's just the figure for beta kit which is synchronized to a lower frequency of GPU, but I don't know the exact clockspeed of Xenon beta kit GPU, does anyone know details about this?

Nikkei Tech-on has an article about the exibition by NEC Electronics at PROTEC JAPAN 2005 which was held along with CEATEC JAPAN 2005 at the same venue from Oct. 5. The short article features Xenos.

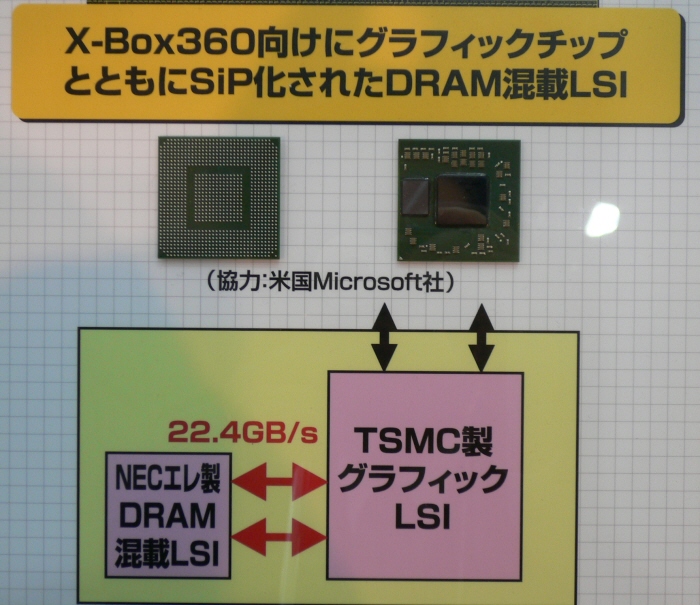

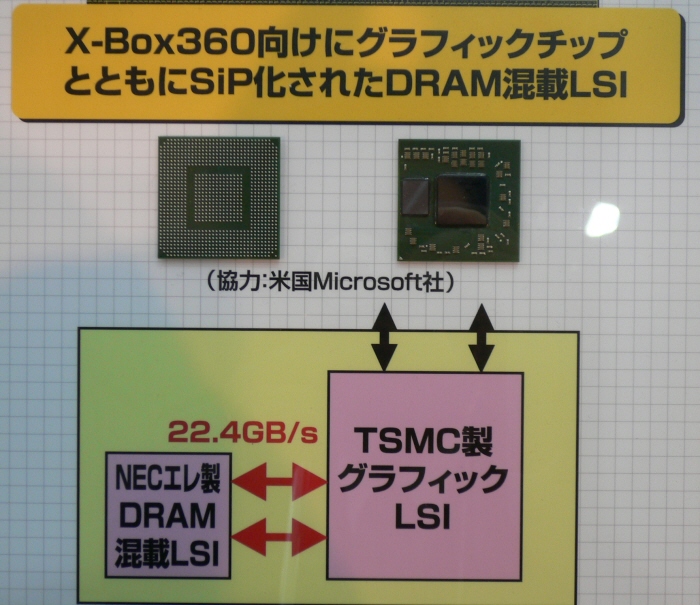

The article was published at Oct. 5 and when I first saw it I thought it's an error though the picture of the material provided by NEC clearly says it's 22.4GB/sec, not 32GB/s. Then later, a correction was added to the article,article said:NEC Electronics exhibited the SiP (System in Package) developed for Microsoft Xbox 360 next-generation home game console at PROTEC JAPAN 2005 at Makuhari Messe from 2005/10/5.

It contains a DRAM-embedded LSI made by NEC Electronics and a graphics LSI made by TSMC in Taiwan in one package. Those bare LSI chips are laid horizontally in a package. Specifically, the graphics LSI and the DRAM-embedded LSI are connected to interposers in a package with flip chips. The reason why NEC Electronics adopted flip chip to connect them is to improve the data transfer speed between chips. In Xbox 360, the maximum data transfer speed required between the DRAM-embedded LSI and the graphics LSI is rather high at 22.4GB/sec. According to NEC Electronics, to achieve this transfer speed, they passed up wire-bonding which is popular for in-package wiring as wire-bonding results in too big wiring inductance. The work for making them in SiP is done by Microsoft.

So apparently NEC reviewed the article after it's published but the 22.4GB/sec figure stayed unchanged.correction said:Though we first wrote "The work for making them in SiP is done by NEC" in this article by an interview at the event, we were informed by NEC Electronics that it's actually done by Microsoft. The article was changed according to this information.

Though 22.4GB/s looks enough already, is there any impact of this downspec on game development? Another possible theory is it's just the figure for beta kit which is synchronized to a lower frequency of GPU, but I don't know the exact clockspeed of Xenon beta kit GPU, does anyone know details about this?