DeadmeatGA

Banned

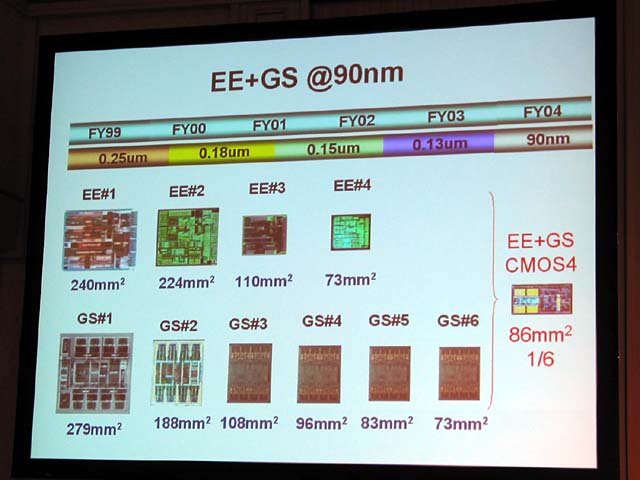

Sony EE gate density

0.250 um : 13 million / 224 mm2 = 0.058 million/mm2

0.180 um : 13 million / 110 mm2 = 0.118 million/mm2

0.150 um : 13 million / 73 mm2 = 0.178 million/mm2

0.090 um : 13 million / 42 mm2 = 0.310 million/mm2

0.065 um : ~ 0.594 million/mm2

Based on this Sony processor gate transistor density calculation of 0.594 million/mm2 at 65 nm, let's presume that Sony reaches for the max and shoot for a 280 mm2 chip, the largest Sony could swallow for consumer application.

280 mm2 * 0.594 million/mm2 = 166.32 million transistors

Meaning SCEI has a maximum budget of 166 million transistors for EE3 if it is to be built like previous EE, with lots of FPUs and little memory.

Now, does 166 million transistors sound enough to pack 4 PPC cores and 32 VUs??? Of course not. This is why I suspect that PSX3 CPU will have a single or dual CELL cores, not quad-core as many speculate. EE3 will never reach 1 teraflops even in the lab, mark my word on it.