You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

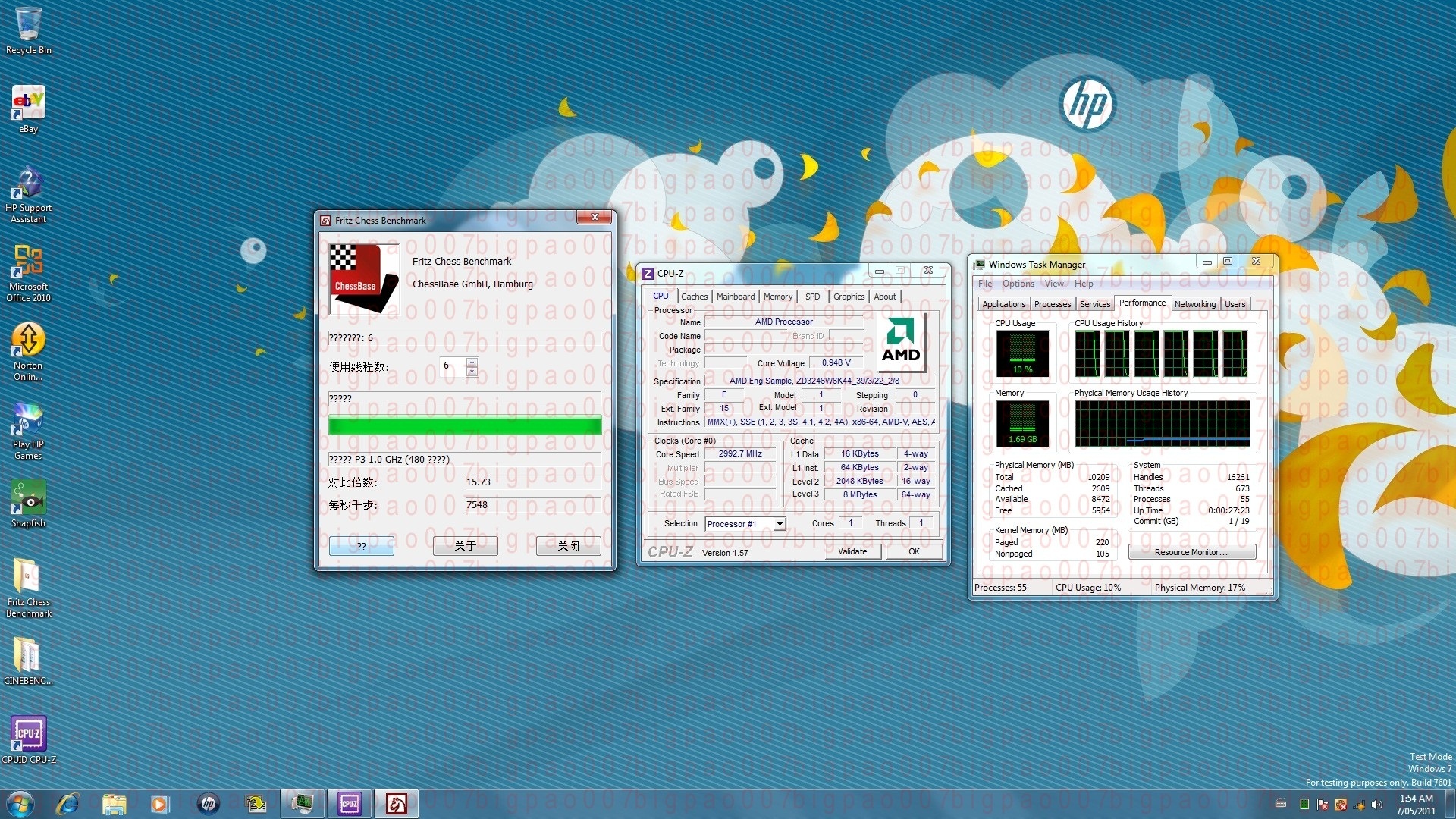

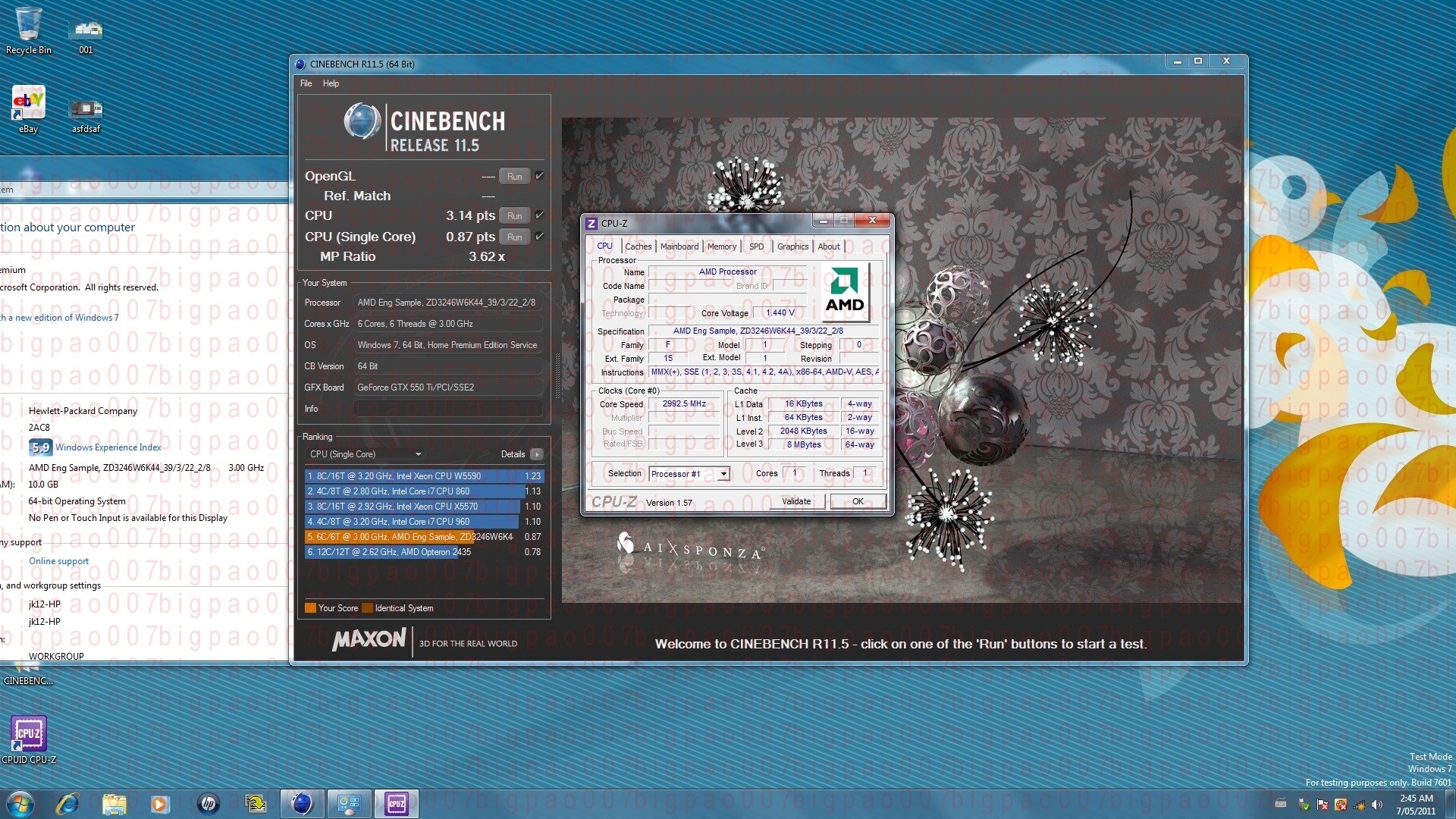

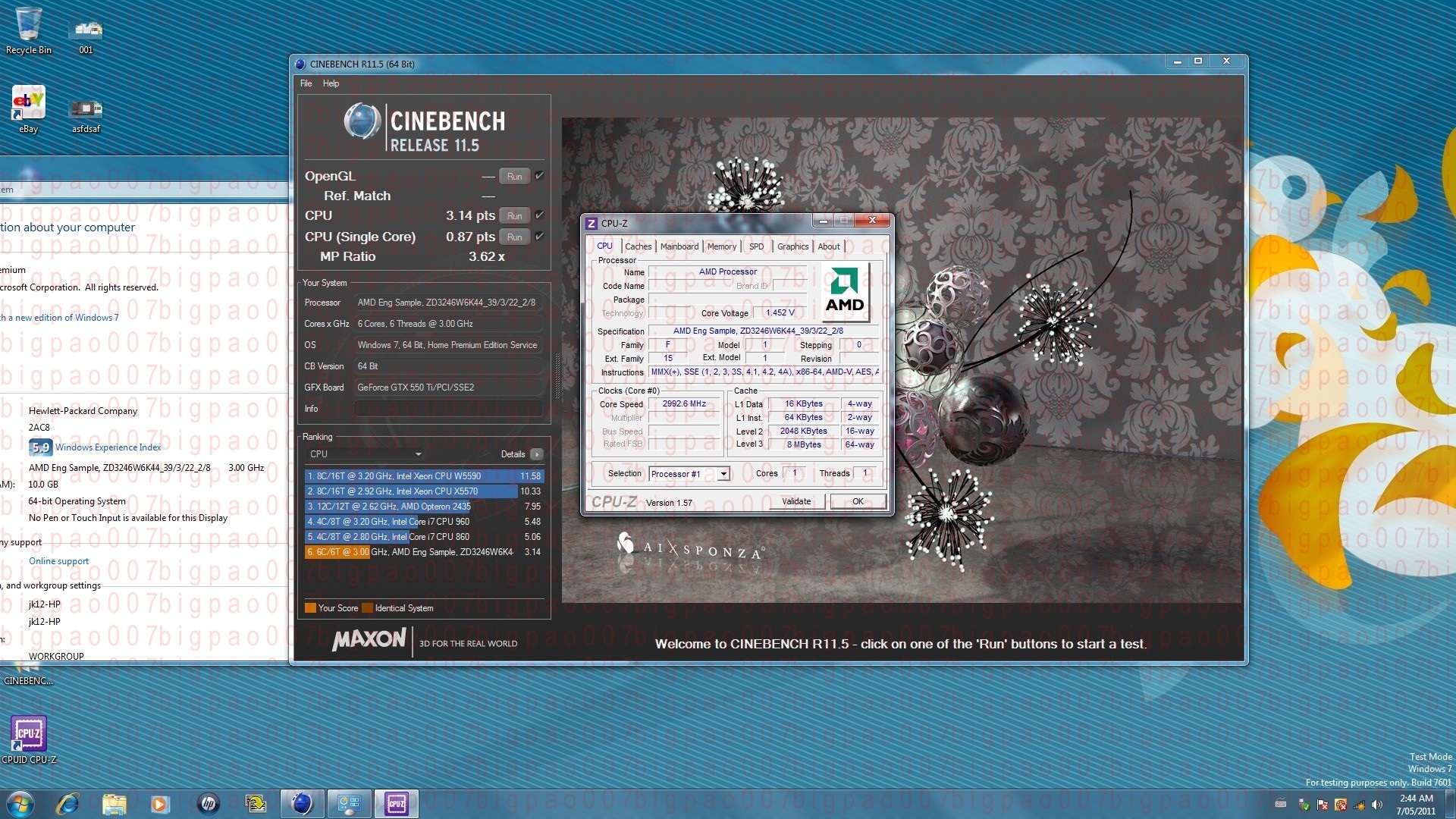

There's definitely something fishy here as when I posted yesterday the link you gave mentioned the model number as ZD282046W6K43 and that was also shown in the charts yet now both the pics and the text seem to refer to ZD282051W8K44. Unfortunately I didn't check yesterday the info in CB10 shot but still...

Perhaps the NB clock is that low?

The BD scores in the benchmarks were low, but my gut reaction is that they would be substantially worse if the cores fell short of their clocks by over 3x.

The BD scores in the benchmarks were low, but my gut reaction is that they would be substantially worse if the cores fell short of their clocks by over 3x.

No. 4-way L1D is official (in the programming guide). Not sure how cpu-z determines this...2-way L1D?

Overall though caches look indeed rather "cheap" (small, not so great latency and associativity isn't really outstanding neither).

No. 4-way L1D is official (in the programming guide). Not sure how cpu-z determines this...

Propably by code which looks like

if (cpumfg == "AuthenticAMD" )

{

L1assoc = 2;

}

I thought it had code to figure it out empirically. But it's always possible such a test turns out the wrong result.Propably by code which looks like

if (cpumfg == "AuthenticAMD" )

{

L1assoc = 2;

}

Hmm right that should be easier and more reliable. Not sure why it would decode it wrong, though I think there have also been cpu errata's about this instruction so it could simply be wrong (especially since this is presumably still non-final silicon).you can determine the associativity with the CPUID instruction. Id be surprised if CPU-Z would do something else.

Overall though caches look indeed rather "cheap" (small, not so great latency and associativity isn't really outstanding neither).

The 2MB L2 cache per module is not small by any means. Intels core-i has just 256 KB L2 per core.

You are of course right - I was more thinking about L1 caches (though it should be noted such a large L2 cache along a L3 cache probably only makes sense if it's exclusive).The 2MB L2 cache per module is not small by any means. Intels core-i has just 256 KB L2 per core.

L1I is 64KB, 2 way (same as earlier AMD cpus). Sandy Bridge only has 32KB L1I, but it only has to feed one "core" (+HTT) and it's 8-way associative.

Sandy Bridge L1D is 8-way 32KB which I guess is similar to 2x16KB 4-way in the end (but again, BD has to feed 2 cores).

L2 is the only cache level where AMD has a size advantage (and a huge one at that - well since L3 is exclusive that at least translates to overall larger cache), though it's only half as fast as SB. It is indeed interesting the size got increased compared to previous generations (which only had 512KB if they also had L3 cache - associativity stayed the same, however). I believe intel still also has more bandwidth between the caches but I'd need to dig up the numbers.

With GPU integration in the future the 2MB L2 cache could be even more usefull. With GPU trashing the L3 it will be better to keep more things in L2 cache.

Are there any sandy bridge benches with HD3000 running in the backround

The first bulldozer fusion parts in 2012 will be dual modul without L3 it seems. Intel cant release a i-core without L3 so that adds die size. While the bulldozer module alone is quite compact and has already 2MB L2 cache.

So it seems they increased the L2 cache with fusion parts in mind.

Are there any sandy bridge benches with HD3000 running in the backround

The first bulldozer fusion parts in 2012 will be dual modul without L3 it seems. Intel cant release a i-core without L3 so that adds die size. While the bulldozer module alone is quite compact and has already 2MB L2 cache.

So it seems they increased the L2 cache with fusion parts in mind.

Last edited by a moderator:

Intel's arcitecture already compensates the "mandatory" L3 with a much smaller (and faster) L2, so I don't see a particular problem here, or a definitive advantage for Bulldozer.The first bulldozer fusion parts in 2012 will be dual modul without L3 it seems. Intel cant release a i-core without L3 so that adds die size. While the bulldozer module alone is quite compact and has already 2MB L2 cache.

So it seems they increased the L2 cache with fusion parts in mind.

From that link:

"May be the test software modules for the bulldozer 3 6 core configuration support the poor performance of the current seen here did not seem as modern AMD processor, much like the opening of the three core only. What bulldozers capabilities, is still a mystery.

User bulldozers delivery thanks" (google translation)

My Phenom2 x4 3.4GHz scores 3.88, so yeah, something doesn't seem right.

Edit: Single core I get 1.01

"May be the test software modules for the bulldozer 3 6 core configuration support the poor performance of the current seen here did not seem as modern AMD processor, much like the opening of the three core only. What bulldozers capabilities, is still a mystery.

User bulldozers delivery thanks" (google translation)

My Phenom2 x4 3.4GHz scores 3.88, so yeah, something doesn't seem right.

Edit: Single core I get 1.01

Last edited by a moderator:

DarthShader

Regular

It's still the same borked B0 stepping chip, most likely with BIOS problems too.