I'm curiousThis being said AMD certainly has a couple of aces up their sleeves which they may want to use in AM5

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

AMD Execution Thread [2024]

- Thread starter del42sa

- Start date

- Status

- Not open for further replies.

DegustatoR

Legend

Well, making 2CCD SKUs with 3D cache on both this time has been mentioned already.I'm curious

Another obvious option is to move away from 8C CCDs to 12C or even 16C ones - which should be possible on current production lines.

Upgrading the IOD from the one used in Zen 4 could also bring sizeable benefits in RAM speeds/latencies.

That's off the top of my head.

I thought 16C-32C comes with 2nm. You can't just increase the core count without increasing L3 to compensate the bandwidth requirements. Anybody here knows if these L3 have a scheduler to handle parallel reads if possible(reads, different lines, no write conflicts) for CCDs? At what point does this become a bottleneck?

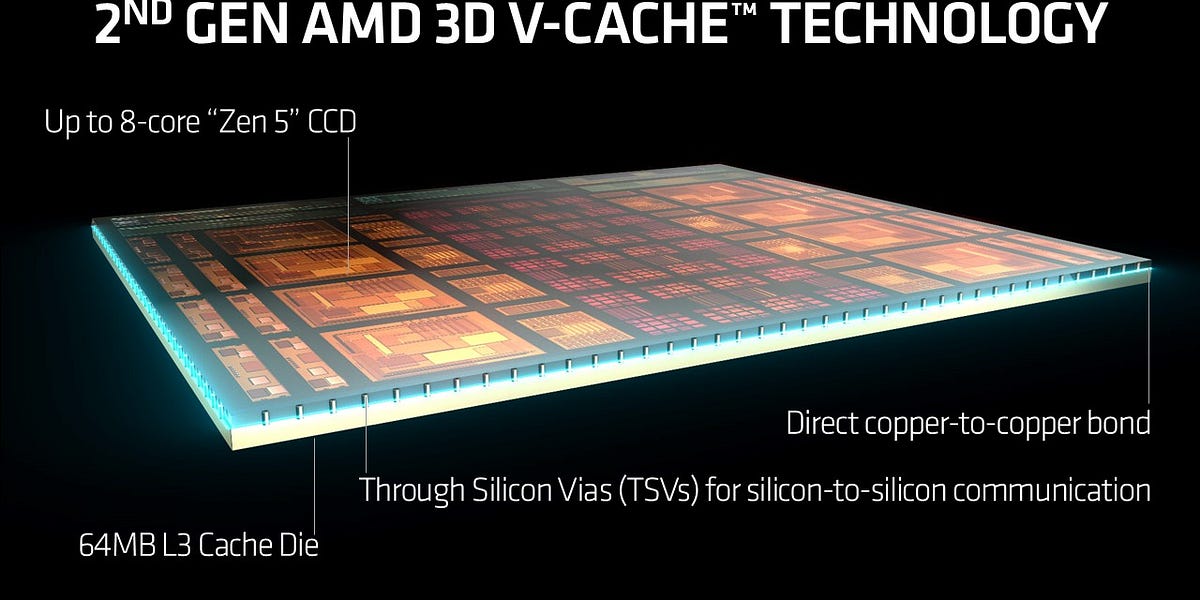

Chips and cheese has a new article talking about 9800X3D's new 3D V Cache:

chipsandcheese.com

chipsandcheese.com

From my understanding, the 3D V Cache is just a capacity expansion over the existing L3 cache, there's no extra port (otherwise it can and should be called a L4 cache).

AMD's 9800X3D: 2nd Generation V-Cache

Following the first generation of V-Cache found in the Zen 3 and Zen 4 X3D SKUs, AMD is now following up with the second generation of V-Cache which is a major change for AMD in terms of packaging.

From my understanding, the 3D V Cache is just a capacity expansion over the existing L3 cache, there's no extra port (otherwise it can and should be called a L4 cache).

Yes, it's just a capacity expansion, exact same cache level.Chips and cheese has a new article talking about 9800X3D's new 3D V Cache:

AMD's 9800X3D: 2nd Generation V-Cache

Following the first generation of V-Cache found in the Zen 3 and Zen 4 X3D SKUs, AMD is now following up with the second generation of V-Cache which is a major change for AMD in terms of packaging.chipsandcheese.com

From my understanding, the 3D V Cache is just a capacity expansion over the existing L3 cache, there's no extra port (otherwise it can and should be called a L4 cache).

I thought 16C-32C comes with 2nm. You can't just increase the core count without increasing L3 to compensate the bandwidth requirements. Anybody here knows if these L3 have a scheduler to handle parallel reads if possible(reads, different lines, no write conflicts) for CCDs? At what point does this become a bottleneck?

Technically 5nm 16C CCDs were already a thing with Zen 4C in Bergamo, though it was a 2 CCX design. And 1 CCX 16C Zen5c CCDs on 3nm are available on Turin dense.

Rumour is 32C Zen6C on 2nm, and that there will also be 8 and 16 core CCDs well, though the rumour didn't specify which type of core. I suspect it might be Zen 6 standard, to enable Venice with 192C (16C x 12 CCDs), and Venice dense with 256 cores (32C X 8 CCDs).

Is an AMD Arm superchip in the works? Fujitsu will partner with Team Red on AI, HPC, open source and Monaka Arm technology

First results from this partnership expected in 2027

DavidGraham

Veteran

ComputerBase compared 7800X3D vs 9800X3D at fixed equal clocks of 4.8GHz and equal RAM speed, the 9800X3D is found to be 15% faster at iso clocks.

www.computerbase.de

www.computerbase.de

AMD Ryzen 9000X(3D) vs. 7000X(3D) bei 4,8 GHz im Vergleich

Warum ist der AMD Ryzen 7 9800X3D in Spielen im Vergleich zum 7800X3D schneller als gedacht? Benchmarks bei gleichem Takt geben Antwort.

DavidGraham

Veteran

AMD is letting go of 4% of it's global workforce to "align AMD resources with our largest growth opportunities".

wccftech.com

wccftech.com

In a statement given to Wccftech, an AMD spokesperson confirmed the layoffs. According to AMD, the layoffs are "a part of aligning our resources with our largest growth opportunities." They are part of "a number of targeted steps that will unfortunately result in reducing our global workforce by approximately 4%." AMD added that it is "committed to treating impacted employees with respect and helping them through this transition."

AMD Confirms Laying Off 4% Of Its Employees To Align Resources With "Largest Growth Opportunities"

Chip designer Advanced Micro Devices, Inc. (AMD) is purportedly laying off 4% of its workforce or 1,000 workers, according to online reports.

Is an AMD Arm superchip in the works? Fujitsu will partner with Team Red on AI, HPC, open source and Monaka Arm technology

First results from this partnership expected in 2027www.techradar.com

The author seems to have made up this statement completely out of thin air. There are some rumours of an AMD ARM APU called Sound Wave (Though I would doubt even that tbh), but there's absolutely nothing to suggest AMD is working on an ARM server chip, nor would AMD have any incentive to compete with its own x86 chips. The article is clear that AMD is only supplying Instinct GPUs and software support.

DavidGraham

Veteran

A new rumor about future AMD GPUs:

-There is no RDNA5 code name. After RDNA4, it will be UDNA.

-MI400 and RX9000 use the same UDNA, and the architecture uses an ALU design similar to GCN.

-UDNA Gaming GPU is tentatively scheduled for mass production in Q2 26.

-Sony's PS6 will use UDNA, and the CPU has not yet been determined to be ZEN4 or ZEN5.

wccftech.com

wccftech.com

-There is no RDNA5 code name. After RDNA4, it will be UDNA.

-MI400 and RX9000 use the same UDNA, and the architecture uses an ALU design similar to GCN.

-UDNA Gaming GPU is tentatively scheduled for mass production in Q2 26.

-Sony's PS6 will use UDNA, and the CPU has not yet been determined to be ZEN4 or ZEN5.

AMD UDNA "Radeon" Gaming GPUs Rumored To Enter Mass Production In Q2 2026, Sony PS6 Also Expected To Utilize Next-Gen Architecture

AMD's UDNA architecture-based Radeon gaming GPUs will allegedly enter mass production in Q2 2026 & also be integrated into Sony's PS6.

GCNbros… we are so back.A new rumor about future AMD GPUs:

-There is no RDNA5 code name. After RDNA4, it will be UDNA.

-MI400 and RX9000 use the same UDNA, and the architecture uses an ALU design similar to GCN.

-UDNA Gaming GPU is tentatively scheduled for mass production in Q2 26.

-Sony's PS6 will use UDNA, and the CPU has not yet been determined to be ZEN4 or ZEN5.

AMD UDNA "Radeon" Gaming GPUs Rumored To Enter Mass Production In Q2 2026, Sony PS6 Also Expected To Utilize Next-Gen Architecture

AMD's UDNA architecture-based Radeon gaming GPUs will allegedly enter mass production in Q2 2026 & also be integrated into Sony's PS6.wccftech.com

It’s so interesting to watch this develop. RDNA was supposed to be the great comeback for Radeon, as gaming cards could be untethered from DC designs. However I guess that makes little sense as very few bought into RDNA.

If Sony is going for UDNA why would they use by all means ancient CPUs to accompany it? There will be at least Zen 6 ready in similar timeframe, if not Zen 7.-Sony's PS6 will use UDNA, and the CPU has not yet been determined to be ZEN4 or ZEN5.

Console APUs tend to be extremely die size (manufacturing cost) constrained, and I wouldn't be shocked if they were targeting a node or 3 down from the bleeding edge, along with the CPU designs to match. Newer cores in general tend to require more transistors every generation. I could see them going Zen4c or Zen5c for that time frame and whatever the most budget friendly 3nm-class node there is on offer.If Sony is going for UDNA why would they use by all means ancient CPUs to accompany it? There will be at least Zen 6 ready in similar timeframe, if not Zen 7.

GCNbros… we are so back.

It’s so interesting to watch this develop. RDNA was supposed to be the great comeback for Radeon, as gaming cards could be untethered from DC designs. However I guess that makes little sense as very few bought into RDNA.

Hmmmm it’ll definitely be interesting to see how this unified arch plays in games. With RT and upscaling becoming more prevalent shaders are likely to get even more branchy.

Will UDNA stick with 64-wide wavefronts executed over 4 clocks?

This looks to be MI300C, which was rumoured to be cancelled. I think they are going for only GPU/AI based chiplets for the next gen MI series though, no more CPU hybrids.

Console APUs tend to be extremely die size (manufacturing cost) constrained, and I wouldn't be shocked if they were targeting a node or 3 down from the bleeding edge, along with the CPU designs to match. Newer cores in general tend to require more transistors every generation. I could see them going Zen4c or Zen5c for that time frame and whatever the most budget friendly 3nm-class node there is on offer.

Yep, people forget that the PS5 and Xbox Series X/S in late 2020 used a Zen 2 mobile implementation (essentially a "c" version with half the L3) even though Zen 3 was out by that time. And the SoCs were on 7nm even though Apple was shipping 5nm by then. Zen 5c wouldn't be a surprise considering the die size is very similar to Zen 4 as Zen 6 would presumably increase the die size a fair bit. The GPU IP is likely to be newer as it is larger and needs to be more area efficient IP. Agreed on the node as well, N2 or newer would be too expensive for anything except AI/HPC or flagship SoCs. I would expect the next gen console chips to be on a density optimized 3nm node, possibly N3S.

arandomguy

Veteran

In general I'm not to sure how relevant "bleeding edge" CPU performance is for a console. We kind of want them on the PC for gaming because we're trying to basically brute force games optimized to 60 (or 30) fps to higher frame rates.

A PS6 would likely be designed more so with VRR in mind and have other techniques to aim for 60 fps and higher in terms of playable stability. Another 20% faster CPU or whatever is not likely to be the limitation.

If cross gen is also going to be the focus then you can't really design the core gameplay around a much faster CPU either as that wouldn't scale backwards to the PS5/pro.

Also as mentioned somewhat above it's worth keeping in mind Zen 2 APUs on the consoles are actually rather slow/behind. Zen 4 (or 5) by itself is a rather significant 50%+ increase already depending on the implementation context. The general direction also is likely to move more off to the GPU or even other dedicated units (eg. decompression this gen).

A PS6 would likely be designed more so with VRR in mind and have other techniques to aim for 60 fps and higher in terms of playable stability. Another 20% faster CPU or whatever is not likely to be the limitation.

If cross gen is also going to be the focus then you can't really design the core gameplay around a much faster CPU either as that wouldn't scale backwards to the PS5/pro.

Also as mentioned somewhat above it's worth keeping in mind Zen 2 APUs on the consoles are actually rather slow/behind. Zen 4 (or 5) by itself is a rather significant 50%+ increase already depending on the implementation context. The general direction also is likely to move more off to the GPU or even other dedicated units (eg. decompression this gen).

- Status

- Not open for further replies.

Similar threads

- Replies

- 30

- Views

- 3K

- Replies

- 39

- Views

- 7K

- Replies

- 17

- Views

- 4K

- Replies

- 4K

- Views

- 532K

D