„Spit out„ sounds More like after all things done you get 2 out. @Ryan Smith can you clear this?

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Intel ARC GPUs, Xe Architecture for dGPUs [2018-2022]

- Thread starter DavidGraham

- Start date

-

- Tags

- intel

- Status

- Not open for further replies.

Megadrive1988

Veteran

The Intel Xe-LP GPU Architecture Deep Dive: Building Up The Next Generation

https://www.anandtech.com/show/1597...tecture-deep-dive-building-up-from-the-bottom

https://www.anandtech.com/show/1597...tecture-deep-dive-building-up-from-the-bottom

My understanding is that it's after culling, so 2 backface culled primitives per clock.„Spit out„ sounds More like after all things done you get 2 out. @Ryan Smith can you clear this?

For reference, here's the exact text on the spec for Gen11, which was 1/cycle: "Primitive / Clock (backface Cull - strips)"

Thank you @Ryan Smith. Sorry but i'm not a native englisch speaker. I don't get it. So this mean after Culling you get 2 Primitives. Does this mean they have 2 Rasterizer? Or is it befor Rasterizer. Thank you in advanced!

The rasterizer converts continous geometry information into the pixel raster, hence the name. It's capabilities are mostly measured by how many pixels per clock it puts out, normally not by how many different triangles they can belong to.

edit: Very late edit after thread split: Please see here as well where I expand a little on what should have been in this very post from the beginning.

edit: Very late edit after thread split: Please see here as well where I expand a little on what should have been in this very post from the beginning.

Last edited:

Recent discussion split to https://forum.beyond3d.com/threads/modern-and-future-geometry-rasterizer-layout-spawn.61972/

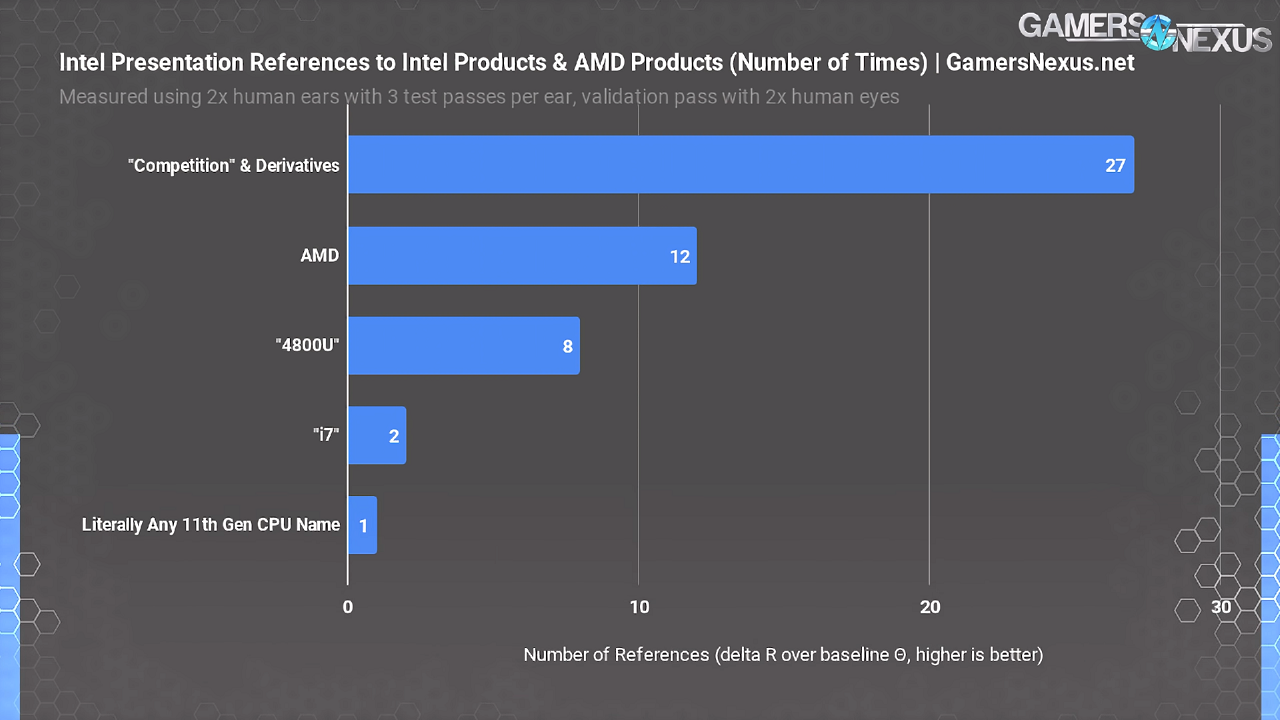

Yeah. Terrible timing, or maybe on purpose? From the couple of videos I've watched reviewing the presentation, it was a rather pathetic release.Funny Intel had a tiger lake event with new gpu an here is total silence

The start of Gamers Nexus video was rather funny.

The start of Gamers Nexus video was rather funny.

I've certainly been made aware of the Renoir 4800U and how it competes with the 11th gen 11... the 116... Was there a letter in there? 11486Ö? Yea, sounds about right.

Seriously though. I can't really fathom the potential customer who'd ever go "Oh they're talking shit about the competition, this is a company I can trust to deliver". Then again I'm equally stumped when the same pattern repeats elsewhere, so maybe I'm just not very good at this "human" stuff.

As to the product, I just want it in testers hands to get an iGPU vs iGPU test done. I'm low-key excited about Xe. More competition in the space will be interesting.

Yeah. Terrible timing, or maybe on purpose? From the couple of videos I've watched reviewing the presentation, it was a rather pathetic release.

The start of Gamers Nexus video was rather funny.

Please no memes. Lets stick with benchmarks.

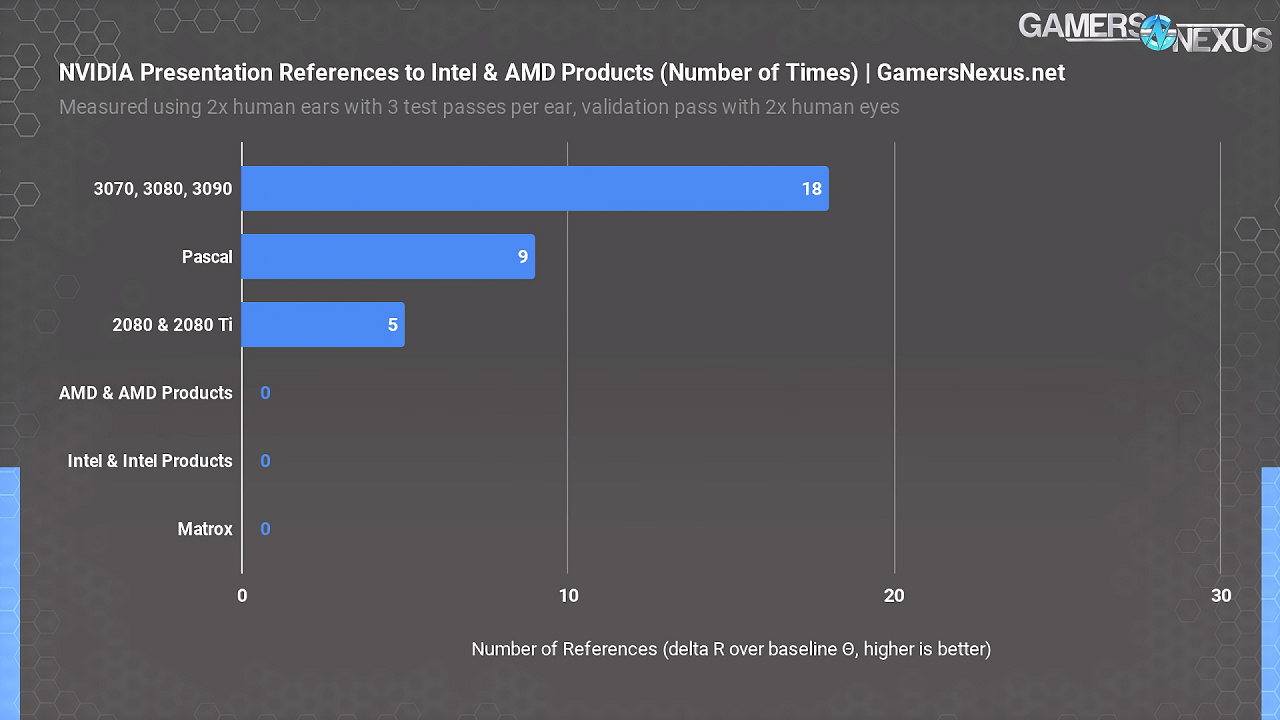

Matrox. Now that is a name I've not heard in a long time. A long time.

Matrox G400 Max, that brings back memories.

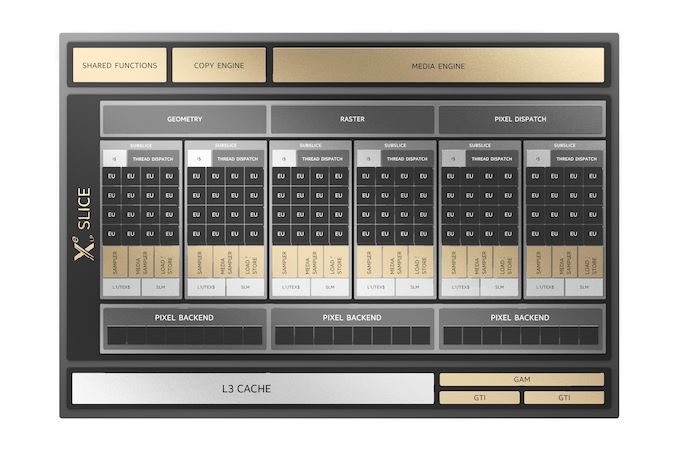

X^e LP looks like single Rasterizer.

https://pics.computerbase.de/9/4/3/2/1/10-1080.28ff95ba.png

https://pics.computerbase.de/9/4/3/2/1/10-1080.28ff95ba.png

There is an argument for there being at least as much pixel throughput in the pixel back end as the rasterizer is capable of emitting. A mismatch wouldn't necessarily break anything, but could lead to underutilization or stalls depending on which way the imbalance goes.Thankt you CarstenS! In this picture it looks a little bit strange. You have 3 pixel Backends for 2 Subslices that means normaly that you have also 3 rasterizer?

Having one rasterizer could make it simpler to have mismatched counts, since there's no uncertainty on the part of the rest of the pipeline about which rasterizer is responsible for a given tile. Having multiple rasterizers could make it easier to match the raster/RBE throughput, but depending on how processing is handled it might require extra work or communication between front ends when geometry processing applies to more than one tile (triangle crossing boundaries, tessellation output from one execution unit needing to flow to arbitrary front ends, etc.).

Being typically at the end, ROPs would have these questions already resolved.

That seems to be an area of complexity in how AMD managed its multiple rasterizers in past generations. The unification of certain parts of the front end in RDNA may be in part due to improving potential weak points in making multiple rasterizers with mostly equal levels of authority but possibly uneven methods of cooperation.

XE-HPG may have 960 EUs. If it's like in the architecutre below you will have 5 double dies. So up to 10 slices.

source:

https://videocardz.com/newz/intel-xe-hpg-graphics-cards-rumored-to-offer-up-to-960-eus

source:

https://videocardz.com/newz/intel-xe-hpg-graphics-cards-rumored-to-offer-up-to-960-eus

Last edited:

- Status

- Not open for further replies.

Similar threads

- Replies

- 487

- Views

- 75K

- Replies

- 211

- Views

- 6K

- Replies

- 3

- Views

- 971