Panajev2001a

Veteran

Jaws said:one said:This is reminiscent of BlueGene/L, as its single compute node has a mini-kernel (CNK) running on it.

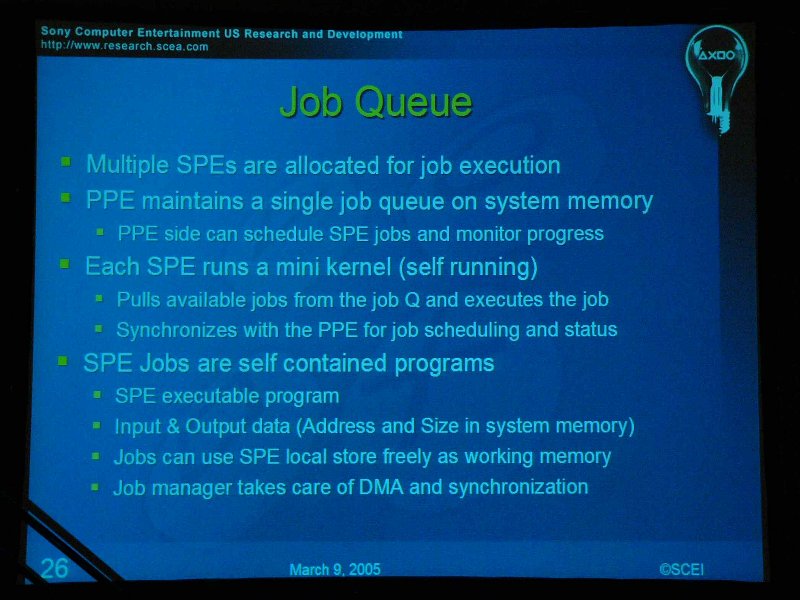

Each SPE runs a mini- kernal

As I predicted they would run some sort of nano-kernel ala TAOS,

TAOS: http://www.byte.com/art/9407/sec6/art1.htm

Jaws said:...

They get around the uniform ISA problem in a heterogeneous multi-processor environment by compiling to a 'virtual' processor with no overheads in translation due to a very efficient nano-kernel running on each processor. I know the CELL press releases mentions that the CELL processors can run multiple operating systems. If this means multiple nano-kernels or equivalent on each core, then they could be borrowing many ideas from TAOS for CELL.

...

http://www.beyond3d.com/forum/viewtopic.php?p=438987#438987

Hannibal in the article below mentions that SPEs can have various scaler and vector configurations,

http://arstechnica.com/news.ars/post/20050308-4685.html)

Hmm...So we're still on for a CELL Virtual Machine, i.e. CELL VM ISA?

You can run a VM, if you want.

I do not think the micro-kernel is there as a VM: it is more like a local work scheduler. Remember that patnet by Gschwind about overlays and the need for a global module which would take care of loading on a need basis the chunks of overlay you need ?

Surely though you can implement your mini-VM idea to virtualize the SPE.

They mention the idea of using the SPE's to run VM's on there as an example on how to use them. We will see though, I am not excluding your idea completely.

hannibal's comment was talking about changing the Hardware lying inside, but letting the ISA stay the same: we still ahve to see what is exposed in the ISA and what is not. About GPR's, you could nto increase their number unless you implemented some kind of Register File rotation or Register Renaming mechanism.

The Taos operating system uses objects from the ground up to enable processors based on different architectures to work together on the same problem/This is not CELL's problem though.