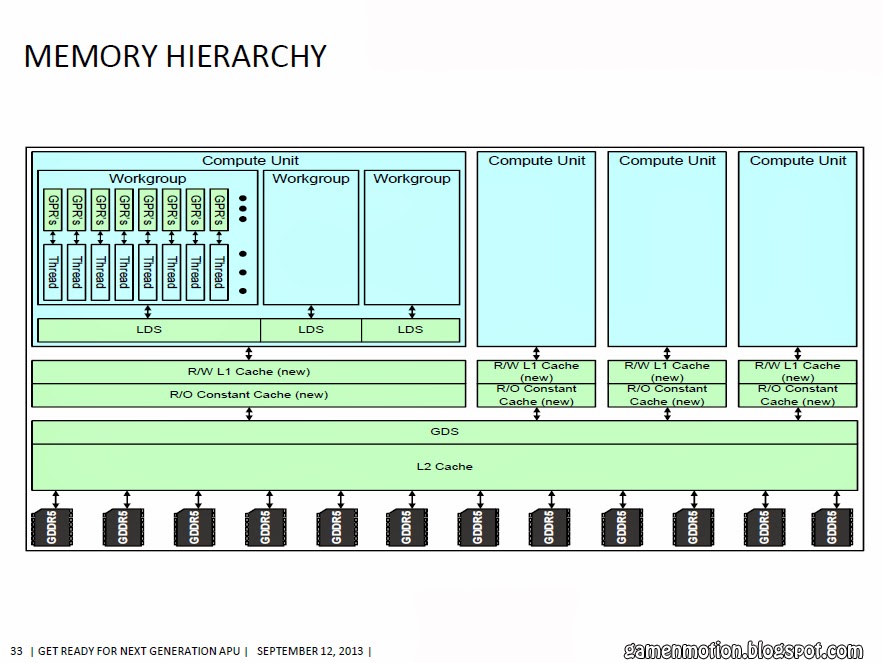

PS4 Liverpool APU & AMD Kaveri APU seem to have a few things in common.

Here is the Kaveri PDF. http://share.csdn.net/uploads/5232b691522ba/5232b691522ba.pdf

Here is the Kaveri PDF. http://share.csdn.net/uploads/5232b691522ba/5232b691522ba.pdf