Perhaps he is in a process of preparing to write his article or just writing it now.

Don't get your hopes up , a 100% increase in performance on the same process will never happen , even a 60% sounds pretty far fetched , these are the kind of vaguely written statements directed at ill informed people to make the writer sound deeply informed .

A change in the arrangements of shader clusters will impose heavy modifications on the front end just to cope with the change , let alone increase performance .

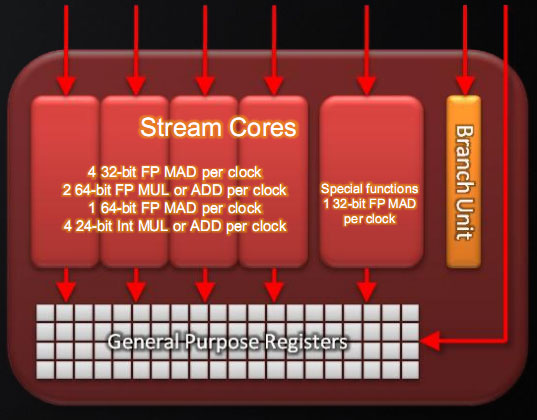

Shaders are not the only logic responsible for increasing performance , there are other factors too , texturing , fill rate , z -sampling , interpolation , improvements in these areas require die area , if you cut corners there the chip will be unbalanced , and you will quickly add bottlenecks to the chip , possibly neutralizing any advantage you have in the shaders .

Of course , there is the possibility of increasing effeciency , but first you have to assume that Evergreen is terribly ineffecient for them to have any significant effeciency gains over the last generation , and improving effeciency isn't some easy and magical process , it is usually restricted by numerous factors , and usually results in small performance gains (5~10%) .

We are all expecting a 30~50% performance improvements for NI over EG , (by using 4D shaders and increasing core & TU count ) but only with 10~20% die increase ? that is outright ridiculous and far fetched , this is not wonder land , this is the real world .