cheapchips

Veteran

Why does anybody pay attention when any of these "news" outlets mention "yields". What yields? For which parts?

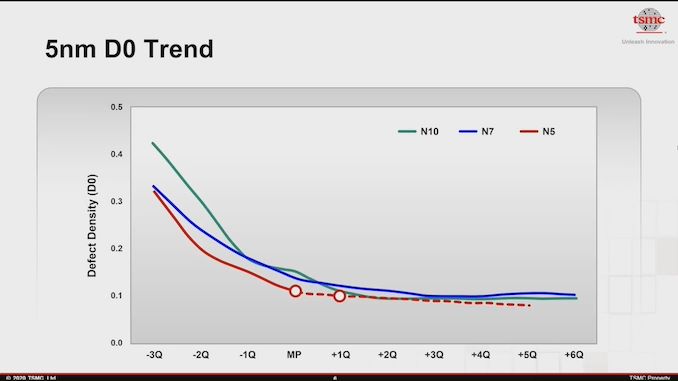

Intel has publicly mentioned that the D0 for 18A is under 0.4, and at that point it was like a year to mass production. For comparison for TSMC, D0 for N5 and N7 was ~0.3-0.35 at 3Q before mass production.

Because they have no idea what they're talking about, like me!