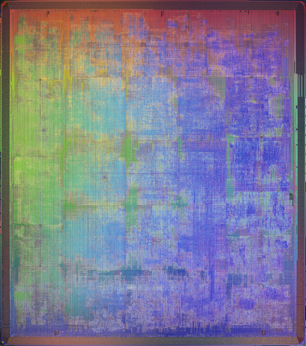

Look at this big 222 million transistor chip.....

- Thread starter Deadmeat

- Start date

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

Oddly enough, the transistor density of this IBM 130 nm process is HIGHER than SCEI's alleged "90 nm" process. So don't keep your hopes too high on SCEI fabs....Using .13, you forgot to note that, but I know what your trying to get at DM

That's becauseAlso considering that the EE+GS@90nm has 4MB of eDRAM which has higher density than logic, that 130nm process seems even better than I thought.

Deadmeat said:That's becauseAlso considering that the EE+GS@90nm has 4MB of eDRAM which has higher density than logic, that 130nm process seems even better than I thought.

1. SCEI's design capability lacks behind indsutry leaders.

2. SCEI's fab capability lacks behind industry leaders.

And some Sony fans want us to believe that SCEI would pull off what Intel and IBM could not, a half a billion transistor clocking at 4 Ghz and burning so little power, yet produced inexpensively...