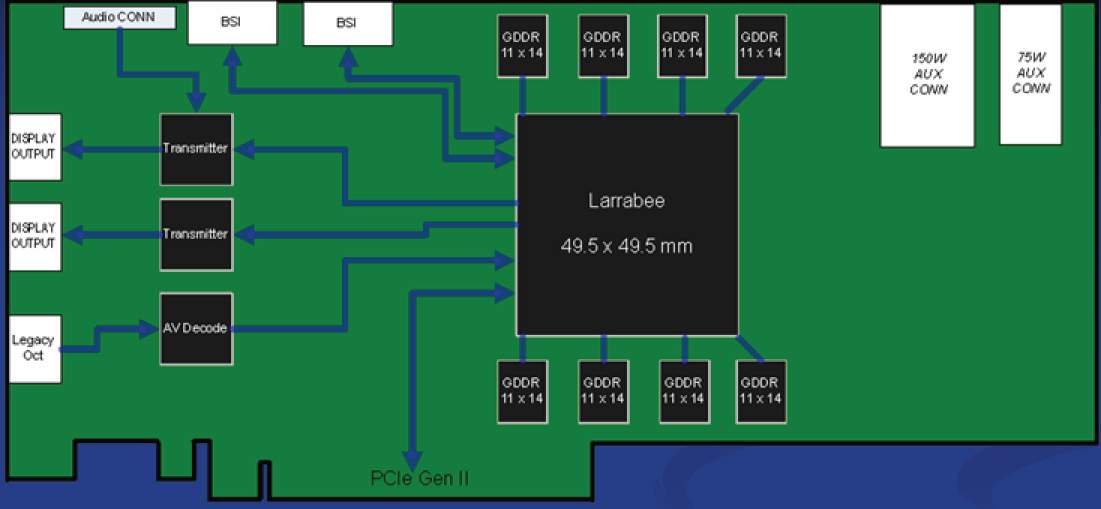

It is amazing how much information is out there in the wild, when you know where to look. TG Daily has just published an article partially based on a presentation they were tipped off about, and which was uploaded on the 26th of April. It reveals a substantial amount of new information, which we will not focus on analysing right now, so we do encourage you to read it for yourself.

Read the full news item

NOTE: Please discuss the architectural info on Larrabee in this thread, and the industry speculation TG Daily's article has in that other thread.

Read the full news item

NOTE: Please discuss the architectural info on Larrabee in this thread, and the industry speculation TG Daily's article has in that other thread.