Forget smartphones or tablets, can anyone tell me what's the point of a quad core even in anything but a laptop/desktop? It sounds pointless even in the former if you ask me.

In theory, the point is that for workloads that *do* scale with four cores, both perf/watt and perf/mm2 are better. For perf/watt, this is because of voltages: two undervolted cores at 750MHz will take a lot less power than one overvolted core at 1.5GHz. For perf/mm2, this can be seen with the Cortex-A15 which is nearly twice as big as the A9 but probably 'only' 60-70% faster overall (counting both IPC and frequency on the same process). That's still pretty good scaling, but obviously you'll get diminishing returns the more you try to scale up per-core performance.

I'd prefer a higher clocked and a wider dual core.

I'd definitely prefer that too, but keep in mind that there will not be a single Cortex-A15 application processor taping out for about one year after Tegra3 taped-out. This is simply as high-end as you can get in this timeframe without designing your own CPU ala Qualcomm, except for the lack of NEON presumably. NV is probably right that it's worth the fairly negligible extra silicon even if it's more useful for marketing than real apps. I think there will be big incentives for AAA game developers to exploit those four cores sooner rather than later, though...

I'm more cautious about Tegra4 as they aren't a lead licensee for Cortex-A15 so it'll presumably still be quad-core A9 (perhaps clocked noticeably higher if they go for 28HPM instead of 28LPT though). We'll see...

Exophase said:

How do you know they aren't going to revamp the architecture significantly for OoOE only to remain effectively dual-issue? Cortex-A9 did. Cortex-A15 level is very lofty for a chip that'll be ready in 2011, not to mention a chip that's "75% the power consumption." Maybe it means 75% consumption when clocked to the same performance levels, ie 1/5th the clock speed using the perfect DMIPS core scaling.

That 75% figure nearly certainly means 4x performance/watt, which you obviously don't want to point out that way or people might realise that means up to 1.25x total power

I agree it's an ambitious goal, but presumably they've had a team working on it since before ARM even finished the A9 (not sure if the A15 started as a parallel project though, since the A9 was unusual in being created primarily by the Sophia Antipolis design center), so it's far from impossible.

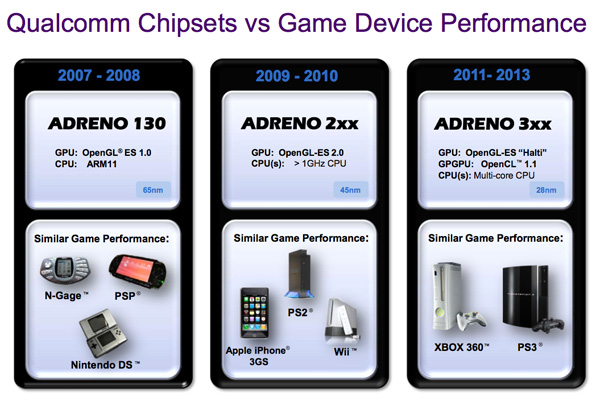

Hard to imagine Qualcomm pushing nearly as much into these markets.

Qualcomm is very ambitious wrt tablets, but obviously they don't care about servers or set-top boxes.

I think the 5x will be more viable with a > 1.5GHz clock than with a Cortex-A15 level architecture. They've already slated 45nm products for 1.5GHz, so wouldn't you expect their 28nm chip to clock higher?

I don't buy it. They achieve 1.5GHz with a high-voltage part for tablets on 40LPT, and there's not a lot of extra performance on the table for 28LPT (20% maybe?). Finally and unlike the A9, they've already got a fairly long pipeline so there's not as much to gain on that front either. It also probably wouldn't be as power-efficient.

It's possible that it's really 4.6x as fast at 1.75GHz, which would get us to a DMIPS/MHz of 2.76 - that's perfectly plausible on a dual-issue OoOE design. Not very exciting though, and I suspect not as likely to be true, but we'll see.