D

Deleted member 13524

Guest

Has anyone seen a review that compares the A10-7850k IGP with a HD7750 GDDR5/DDR3?

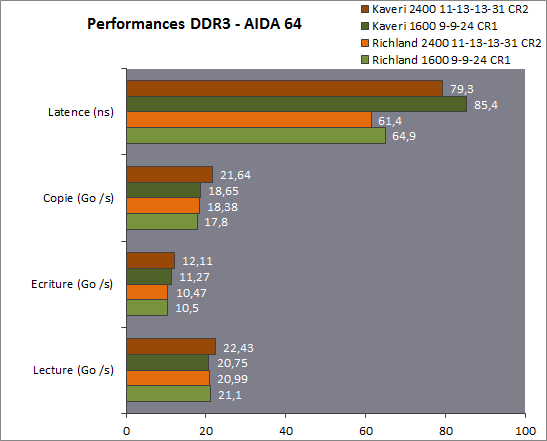

The results are just proof of the Pink Elephant in the Room: lack of memory bandwidth.

The only balanced solution is the A8 with 6 GCN CUs and a 45W TDP.

Above that, increasing the available power and number of CUs is worthless.

And why is there no comment from anandtech or anyone else about the presence of two 128-bit memory controllers in Kaveri?

You mean a LGA-2011 Haswell? They should be coming later this year.

The results are just proof of the Pink Elephant in the Room: lack of memory bandwidth.

The only balanced solution is the A8 with 6 GCN CUs and a 45W TDP.

Above that, increasing the available power and number of CUs is worthless.

And why is there no comment from anandtech or anyone else about the presence of two 128-bit memory controllers in Kaveri?

On the other hand, imagine a native 8 core, 16 thread Haswell with 16MB L3 and no IGP and 150W TDP

You mean a LGA-2011 Haswell? They should be coming later this year.