ltcommander.data

Regular

I'm not an expect on PowerVR nomenclature, so feel free to correct me, but as I understand it USSE is basically a loose term that refers to all the ALUs in a Series5/5XT core. The SGX535 has 2 ALUs and that was an USSE. The SGX540 has 4 ALUs and that was also an USSE.Information is secure.

PowerVR GPU based on 2 vec4 + additional scalar - 4x2+1 = 9.

Now 9 ÷ 8 = 1.125 bonus!

Each core has 2 ALU.

PowerVR G6200 contains 16USSE2 (x2 SGX554).

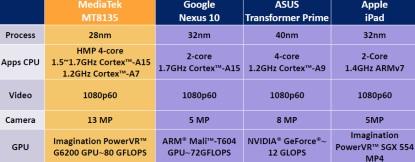

Now 16USSE2 x vec4 x 2 ALU x 2 Core x 1.125 x 0.280MHz ( mhz for MediaTek) = 80GFLOPS.

By simply :

16USSE2 x 2 Core x 0.280 x 9GFLOPS = 80GFLOPS

See more about calculating PowerVR GPU here :

http://www.359gsm.com/forum/viewtopic.php?f=127&t=13396

In an USSE2, each ALU is capable of executing 1 vec4 MAD and a scalar. The 9 FLOPs/ALU comes from a MAD being 2 FLOPs (4 MAD * 2 FLOPS/MAD +1 scalar) not it being capable of 2 independent vec4 + a scalar. So a SGX543MP2 has 2 cores, each with 1 USSE2, with each USSE2 having 4 ALUs, with each ALU having a vec4 unit and a scalar unit. The iPad 2 is usually calculated to be 16 GFLOPs via (2 cores * 4 ALU * 4 MAD/ALU * 2 FLOPS/MAD * 0.25 GHz clock speed) with the scalar unit not usually included in calculations.

PowerVR hasn't said that the USSE2 is being reused in Rogue. In fact, they've indicated Rogue is using scalar ALUs rather than the vector ALUs in the USSE2. Combined with you using the USSE2 term in to refer to a 9 FLOP Series5 XT ALU, I'm not sure what to make of your Rogue calculations.