You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

http://www.zdnet.com/blog/computers...otherboard-for-sandy-bridge-e-processors/6695

Though I think they showed something years ago as well, I think it might have been for the EE Netbursts. I'm not sure if it ever reached retail though.

Though I think they showed something years ago as well, I think it might have been for the EE Netbursts. I'm not sure if it ever reached retail though.

Man from Atlantis

Veteran

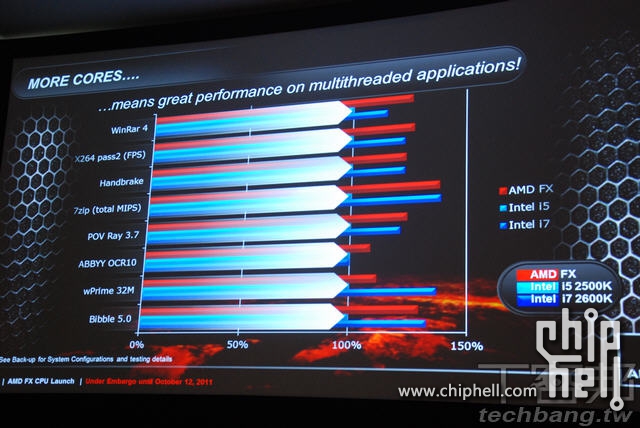

AMD needs 5GHz FX4xxx to match Deneb 3.7GHz

As a desktop CPU with leaked so far performance I can't see it for long at launch price. It's more Core i3 competition and AMD's own 3 core than Deneb improved replacement.

I hope for their sake that server workloads are more forgiving, otherwise another K5

As a desktop CPU with leaked so far performance I can't see it for long at launch price. It's more Core i3 competition and AMD's own 3 core than Deneb improved replacement.

I hope for their sake that server workloads are more forgiving, otherwise another K5

It's a pity they don't preassemble the block with the CPU without a heatspreader, this would be a huge boost in cooling performance.I wonder how good the watercooler is. Generally low-end watercoolers have been significantly worse than good air coolers.

AMD needs 5GHz FX4xxx to match Deneb 3.7GHz

As a desktop CPU with leaked so far performance I can't see it for long at launch price. It's more Core i3 competition and AMD's own 3 core than Deneb improved replacement.

I hope for their sake that server workloads are more forgiving, otherwise another K5

Thats just 2 modules, half BD. The FX4xxx is probably a dirty cheap salvaged SKU.

I think AMD made a mistake to count one module as 2 full cores. People compare 4 core vs 8 core and say its shit. No, it just works as intended and its late to the party.

They may have tried at one point. Some early marketing slides had counted each module as a core, either through an early error or a possible bluff.

Unlike GPUs, the definition of a CPU core is more robust, and there are some notable companies that would be risking many millions of dollars if AMD got away with it.

As the physical path that a thread of execution takes through silicon, the cores in a module are mostly separate, and the parts that are shared are not required to be unique. The instruction issue and control circuits are physically separate.

Unlike GPUs, the definition of a CPU core is more robust, and there are some notable companies that would be risking many millions of dollars if AMD got away with it.

As the physical path that a thread of execution takes through silicon, the cores in a module are mostly separate, and the parts that are shared are not required to be unique. The instruction issue and control circuits are physically separate.

They may have tried at one point. Some early marketing slides had counted each module as a core, either through an early error or a possible bluff.

Unlike GPUs, the definition of a CPU core is more robust, and there are some notable companies that would be risking many millions of dollars if AMD got away with it.

As the physical path that a thread of execution takes through silicon, the cores in a module are mostly separate, and the parts that are shared are not required to be unique. The instruction issue and control circuits are physically separate.

Well average joe will see new uarch cpu beaten by old PIIs and imo this will give really bad impression. Marketing shot in the foot imo.

http://lab501.ro/procesoare-chipseturi/amd-fx-8150-bulldozer-preview

First half-decent benchmark. I wouldn't say the results are too unexpected though I didn't know that cache/memory subsystems really are that bad

First half-decent benchmark. I wouldn't say the results are too unexpected though I didn't know that cache/memory subsystems really are that bad

One curious result that grabbed my attention is the AIDA's Sin-Julia benchmark. This small bench is a pure x87 multi-threaded code that fits entirely in the cache (256KB data per thread). Looks like, contrary to my early assumptions, the legacy FP throughput in BD is much weaker.

DarthShader

Regular

I am hoping somebody (Techreport? Hardware.fr?) will do proper synthetic benchmarking to see where the problem lies. Cause this is definitely not what has been promised (ie. 50% more perf for 33% more cores). Cache subsystem looks like first suspect.

First they didn't specify what clock frequencies they were comparing. Second they dropped it from 50% to something like 33% a few weeks ago.Cause this is definitely not what has been promised (ie. 50% more perf for 33% more cores). Cache subsystem looks like first suspect.

My guess is they hoped to release BD at around 5GHz non-turbo and way over that with turbo but GF manufacturing process wasn't up for the task.

Oops...

SourceActually, we already have such an issue known for Bulldozer, and NO bench-marked system has the patch installed!

The shared L1 cache is causing cross invalidations across threads so that the prefetch data is incorrect in too many cases and data must be fetched again. The fix is a "simple" memory alignment and (possible)tagging system in the kernel of Windows/Linux.

I reviewed the code for the Linux patch and was astonished by just how little I know of the Linux kernel... lol! In any event, it could easily cost 10% in terms of single threaded performance, possibly more than double that in multi-threaded loads on the same module due to the increased contention and randomness of accesses.

Not sure if ordained reviewers have been given access to the MS patch, but I'd imagine (and hope) so! Last I saw, the Linux kernel patch was still being worked on by AMD (publicly) and Linus was showing some distaste for the method used to address the issue. One comment questioned the performance cost but had received no replies... but you don't go re-working kernel memory mapping for anything less than 5-10%... just not worth it!