Jawed

Legend

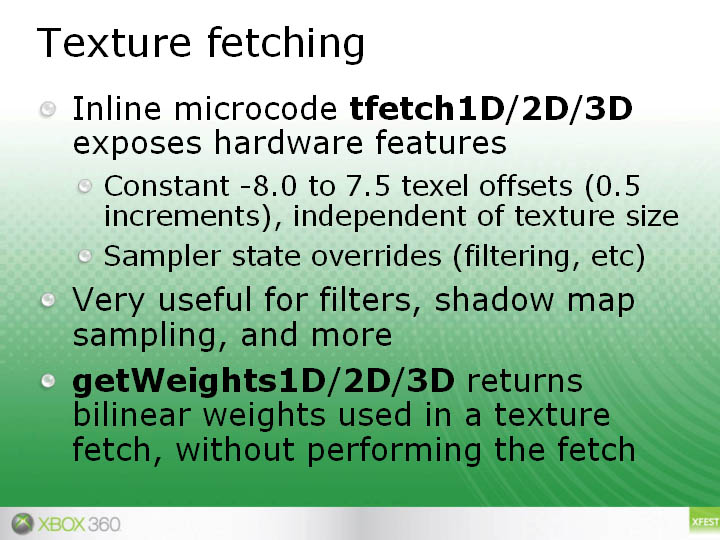

In Xenos there's point-sampling functionality (primarily aimed at vertex fetching) in addition to the normal bilinear (or better) texture fetching/filtering.

Since it's a unified architecture, these point-sampling units are available to any shader concurrently with the bilinear texturing units (erm, I presume they are!). What I'm wondering is, what's the impact going to be on the performance of pixel shading?

It's my understanding that there's generally a fair amount of point-sampled texturing used in pixel shaders, to perform "look-ups". At the same time (not being a dev) I don't know the degree to which point sampling is typically used.

So, will the ability of a pixel shader to perform bilinear (or better) texturing concurrently with point sampled texturing make a signicant performance difference If there are 16 TMUs and 16 TPSs available (texture point samplers, for want of a better abbreviation - perhaps I should just stick to VTF, vertex texture fetch; even if it's a bit confusing because of the context), will this make a significant difference to the performance of pixel shading?

If there are 16 TMUs and 16 TPSs available (texture point samplers, for want of a better abbreviation - perhaps I should just stick to VTF, vertex texture fetch; even if it's a bit confusing because of the context), will this make a significant difference to the performance of pixel shading?

One caveat, as I understand it from Xenos, is that the point-sampling units are really meant for 1D access. I don't know why this constraint exists, or whether it's enforced in any way - it might simply be about performance (e.g. half speed address calculation for 2D textures). I don't know whether it's reasonable to expect this constraint to carry over to future USAs, such as R600.

Jawed

Since it's a unified architecture, these point-sampling units are available to any shader concurrently with the bilinear texturing units (erm, I presume they are!). What I'm wondering is, what's the impact going to be on the performance of pixel shading?

It's my understanding that there's generally a fair amount of point-sampled texturing used in pixel shaders, to perform "look-ups". At the same time (not being a dev) I don't know the degree to which point sampling is typically used.

So, will the ability of a pixel shader to perform bilinear (or better) texturing concurrently with point sampled texturing make a signicant performance difference

One caveat, as I understand it from Xenos, is that the point-sampling units are really meant for 1D access. I don't know why this constraint exists, or whether it's enforced in any way - it might simply be about performance (e.g. half speed address calculation for 2D textures). I don't know whether it's reasonable to expect this constraint to carry over to future USAs, such as R600.

Jawed