A1xLLcqAgt0qc2RyMz0y

Veteran

TSMC Unveils Details of 5nm CMOS Production Technology Platform Featuring EUV and High Mobility Channel FinFETs at IEDM2019

https://semiwiki.com/semiconductor-manufacturers/tsmc/282339-tsmc-unveils-details-of-5nm-cmos-production-technology-platform-featuring-euv-and-high-mobility-channel-finfets-at-iedm2019

https://semiwiki.com/semiconductor-manufacturers/tsmc/282339-tsmc-unveils-details-of-5nm-cmos-production-technology-platform-featuring-euv-and-high-mobility-channel-finfets-at-iedm2019

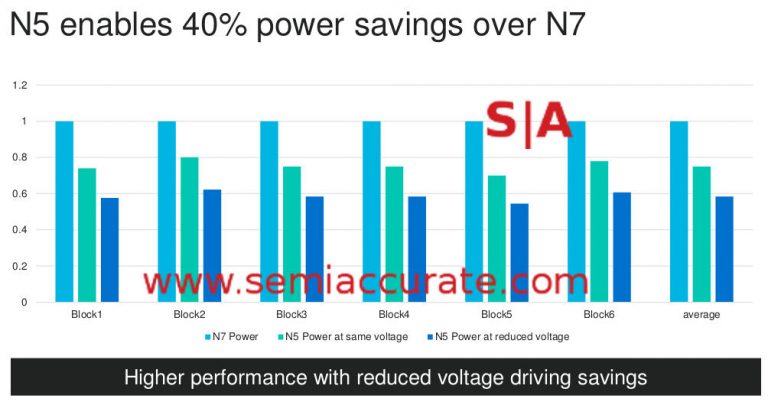

Back in April, 2019, TSMC announced that they were introducing their 5 nm technology in risk production and now at IEDM 2019 they brought forth a detailed description of the process which has passed 1000 hour HTOL and will be in high volume production in 1H 2020. This 5nm technology is a full node scaling from 7nm using smart scaling of major design rules (gate, fin and Mx/Vx pitches) for improved yield featuring an SRAM cell of 0.021um2 and a declining defect density D0 that is ahead of plan.