http://www.aceshardware.com/

So what do u guys think? What major things still need to be overcome in the CPU area? Perhaps they are moving from x86 all together? Any other ideas are appreciated!

P.S

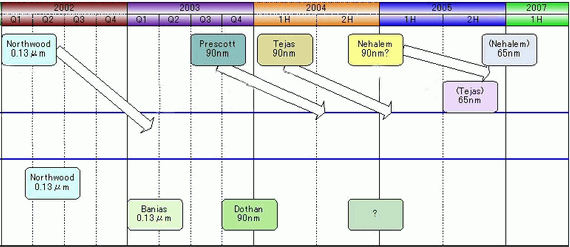

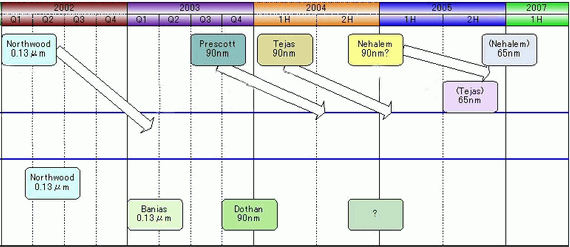

Forgot the roadmap!

Doug Carmean, an architect who worked on the Pentium 4, as well as several other Intel CPUs, makes note of Nehalem in this interview:

RS: What project followed the Willamette project?

DC: I had about a one or two-quarter stay on a project called Prescott, which was a follow-on to Willamette. It was basically doing some performance enhancements and taking it to the next generation process. Within the last year, I’ve been leading the architecture team that’s defining the next all new processor, a processor called Nehalem, and that’s been the focus for the last year. So that could be Pentium 8, or something like that, in the year 2004. So we’re a taking from scratch approach to microprocessor design.

So what do u guys think? What major things still need to be overcome in the CPU area? Perhaps they are moving from x86 all together? Any other ideas are appreciated!

P.S

Forgot the roadmap!