D

Deleted member 2197

Guest

Performance Advisory Issued by AMD for Ryzen 7000 Processors (updted)

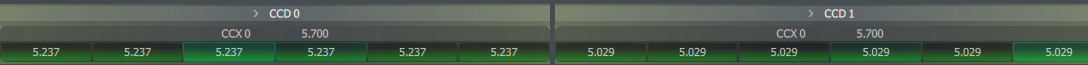

AMD has issued a new advisory regarding the performance characteristics of its new Ryzen 7000 processors, stating that it has received reports of unexpected performance deltas in certain games....