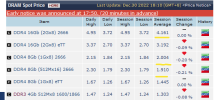

They become unplayable due to VRAM trashing unless they are using the VRAM in a smart way where they just loose some performance. The latter are rare though so generally when you're actually running into VRAM limits you'll see it by results like 0.2 fps.Earlier in the same video lower settings use much lower VRAM though, just rewind

Also game generally don't become "unstable" (well, they shouldn't) when they run out of VRAM, they become slow.

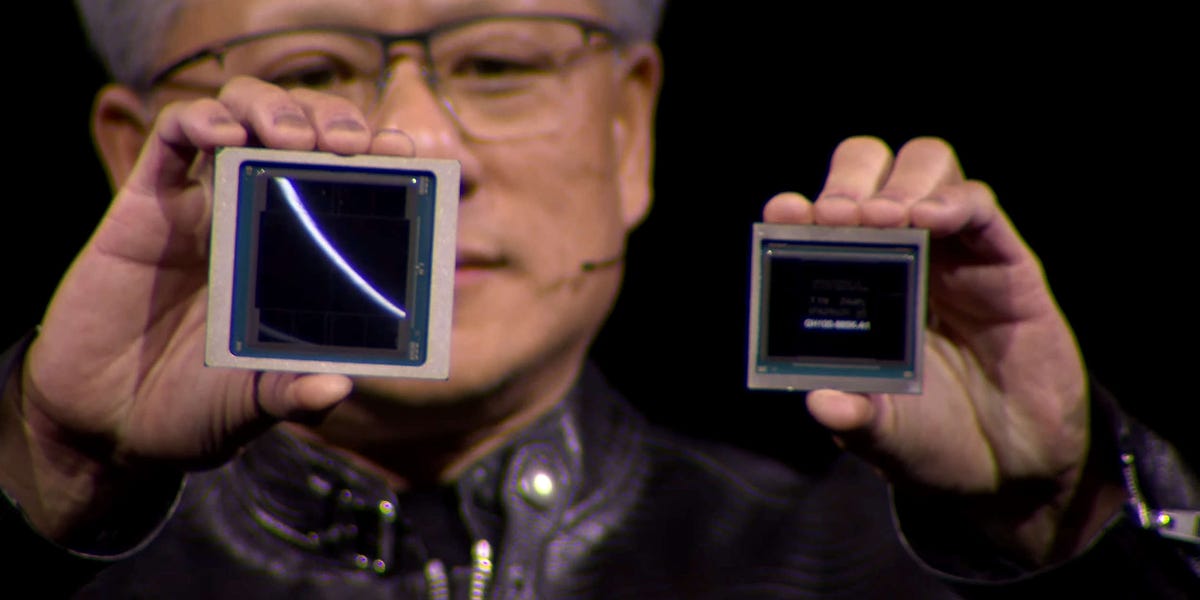

Here's a guy playing Avatar in 4K on a 4080 on Unobtaineoum:

The game a) doesn't seem to consume more than 15GBs of VRAM and b) runs at <20 fps anyway. No VRAM related issues there.

Last edited: