Hi guys,

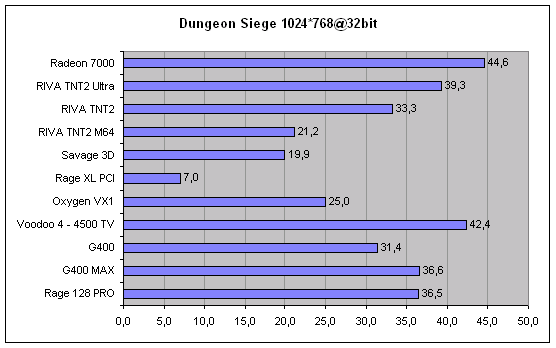

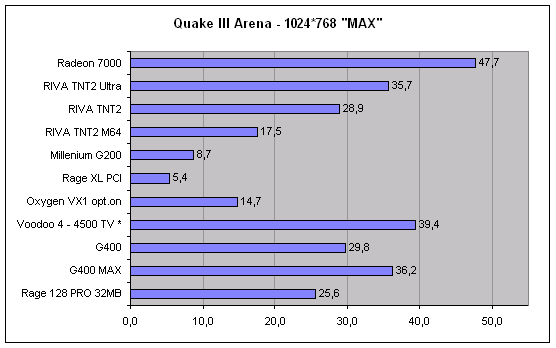

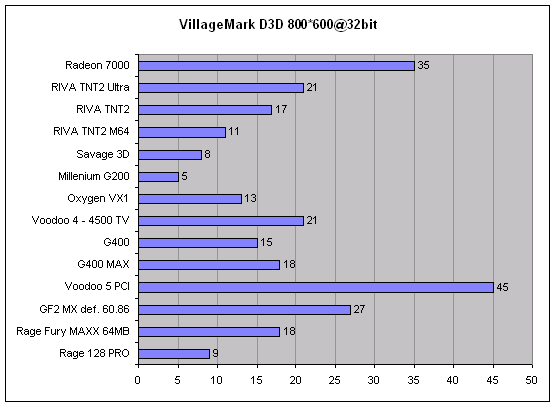

I recently scavenged a nice Radeon VE card for my collection of old computer related junk. Since it turned out it was still working I ran a few benchmarks using an old AGP board with a P4.

I was really surprised to see it was able to score nearly 2800 points at 3Dmark 2001 despite having only one pipeline. It seems that HyperZ is indeed very effective at discarding pixels which are hidden. I don't thin bandwidth is really the limiting factor as it has 2.7GB (as much as a GeForce2MX)

I started looking into this technology but most of the articles or reveiws I found are rather vague. I know that Radeons used both Z compression and Hierarchical-Z technologies.

I'm really intrigued about the hierarchical-Z implementation. There are a few algortihms used for offline rendering but they are rather complex with a pyramidal approach. All I know about the technology used inside the R(V)100 chip is that it caches some kind of Z information for 8x8 pixel tiles. I'm not sure, though, how it effectively works or how big this cache really is, considering that the transistor budget of the day was not very high.

If someone could satisfy my curiosity, I'd be very grateful.

I recently scavenged a nice Radeon VE card for my collection of old computer related junk. Since it turned out it was still working I ran a few benchmarks using an old AGP board with a P4.

I was really surprised to see it was able to score nearly 2800 points at 3Dmark 2001 despite having only one pipeline. It seems that HyperZ is indeed very effective at discarding pixels which are hidden. I don't thin bandwidth is really the limiting factor as it has 2.7GB (as much as a GeForce2MX)

I started looking into this technology but most of the articles or reveiws I found are rather vague. I know that Radeons used both Z compression and Hierarchical-Z technologies.

I'm really intrigued about the hierarchical-Z implementation. There are a few algortihms used for offline rendering but they are rather complex with a pyramidal approach. All I know about the technology used inside the R(V)100 chip is that it caches some kind of Z information for 8x8 pixel tiles. I'm not sure, though, how it effectively works or how big this cache really is, considering that the transistor budget of the day was not very high.

If someone could satisfy my curiosity, I'd be very grateful.