"Nerve-Damage"

Regular

Well judging by how these patents (abstract/context/descriptions) are written up, it would seem they are referring (indirectly) too the RSX GPU.

Follow along with me….

Point A:

Right here Nvidia makes reference too a third type of GPU (third embodiment) currently not available too the market in GPU form.

Point B:

In this Sony/IBM patent they make reference towards the stream processor (RSX?)…quoted below. The CPU> Stream Processor>DMA Controller (or the link between them).

Point C:

In this patent Nvidia is specifically talking about programming (smarter) for a stream processor unit.

Point D:

These two guys (Robin J Green & Gabor Nagy) play a key role in Sony development community; they have worked on previous co-sub projects with Sony. Green by the way has worked/still working with EA.

Anyhow, This patent by them (I can 100% guarantee is based around PS3 development) is dealing with a stream processor: "Method and apparatus for real-time global illumination incorporating stream processor based hybrid ray tracing

".

Please constructive feed back of ideals, thoughts, criticism, or just a general take of the subject.

No lame remarks “PO-LEASE” :smile:

Follow along with me….

Point A:

Right here Nvidia makes reference too a third type of GPU (third embodiment) currently not available too the market in GPU form.

[0035] Likewise, a third embodiment or instantiation of dedicated graphics hardware shall be referred to here as a programmable streaming processor. A programmable streaming processor comprises a processor in which a data stream is applied to the processor and the processor executes similar computations or processing on the elements of the data stream. The system may execute, therefore, a program or kernel by applying it to the elements of the stream and by providing the processing results in an output stream. In this context, likewise, a programmable streaming processor which focuses primarily on processing streams of fragments comprises a programmable streaming fragment processor. In such a processor, a complete instruction set and larger data types may be provided. It is noted, however, that even in a streaming processor, loops and conditional branching are typically not capable of being executed without intervention originating external to the dedicated graphics hardware, such as from a CPU, for example. Again, an embodiment of a GPU with this level of capability or a similar level comprises a programmable streaming processor in this context.

Point B:

In this Sony/IBM patent they make reference towards the stream processor (RSX?)…quoted below. The CPU> Stream Processor>DMA Controller (or the link between them).

9. The method as recited in claim 8, wherein said processing an application comprises processing an application using a processing element selected from the group consisting of: a central processing unit (CPU); a streaming processor; and a DMA controller.

16. The processor assembly as recited in claim 15, wherein each of said processing elements is selected from the group consisting of: a central processing unit (CPU); a streaming processor; and a DMA controller.

[0014] Among the components mounted on the processor assembly 100 are first and second microprocessors 110, 115. As illustrated, each of the microprocessors 110, 115 are single processor chips formed on the chip 105 for performing any of a variety of computing applications. The first microprocessor 110 includes a plurality of processing elements (one of which is designated 120) arranged therein. Likewise, the second microprocessor 115 also includes a plurality of processing elements (one of which is designated 125) arranged therein. Without limitation, each of the processing elements 120, 125 may be a standard central processing unit (CPU), a streaming processor, or a DMA controller. Of course, the invention is not limited to any particular embodiment. Although only two microprocessors 110, 115 are shown in FIG. 1, those who are skilled in the relevant field of art understand that a greater number of microprocessors may be employed without deviating from the principles disclosed herein.

Point C:

In this patent Nvidia is specifically talking about programming (smarter) for a stream processor unit.

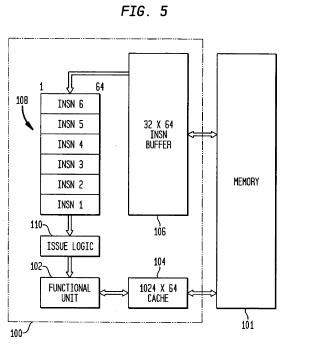

A system optimizes two or more stream processing programs based upon the data exchanged between the stream processing programs. The system alternately processes each stream processing program to identify and remove dead program code, thereby improving execution performance. Dead program code is identified by propagating constants received as inputs from other stream processing programs and by analyzing a first stream processing program and determining the outputs of a second stream processing program that are unused by the first stream processing program. The system may perform multiple iterations of this optimization is previous iterations introduce additional constants used as inputs to a stream processing program. Following optimization of the stream processing programs, the optimized stream processing programs are compiled to a format adapted to be executed by a stream processing system.

[0016] An embodiment of the stream processing system resides within a graphics processing subsystem. In this embodiment, a programmable stream processing unit may be a programmable vertex processor, a programmable tessellation processor, or a programmable fragment processor

[0025] FIG. 1 is a block diagram of a computer system 100, such as a personal computer, video game console, personal digital assistant, or other digital device, suitable for practicing an embodiment of the invention.

[0029] Additional GPUs 155 can be located on the same circuit board as GPU 135 and sharing a connection with GPU 135 to data bus 160, or can be located on additional circuit boards separately connected with data bus 160. Additional GPUs 155 can also be integrated into the same module or chip package as GPU 135. Additional GPUs 155 can have their own display and additional memory, similar to display memory 140 and additional memory 145, or can share memories 140 and 145 with GPU 135. In an embodiment, the graphics coprocessor 165 is integrated with the computer system chipset (not shown), such as with the Northbridge or Southbridge chip used to control the data bus 160.

[0030] FIG. 2 illustrates an example chain of stream processing units 200 of a graphics processing subsystem suitable for implementing an embodiment of the invention. Chain of stream processing units 200 uses a stream-processing model, in which input elements are successively read and operated on by the chain of stream processing units 200. Each stream processing unit of the chain 200 can operate on the outputs of previous stream processing units in the chain. As discussed in detail below, some or all of the stream processing units may be programmable. Programmable stream processing units read an input element, execute a program using the input element, and output the result to the next stream processing unit in the chain. Each stream processing unit can have its own separate program operating independently or in conjunction with another stream processing unit program.

[0035] Although not shown in the example of FIG. 2, additional types of stream processing units can be included in the chain of stream processing units 200. For example, a tessellation processor can receive descriptions of higher order surfaces and produce sets of geometric primitives defined by vertices and approximating or corresponding to the higher order surfaces. The sets of geometric primitives and their associated vertices can then be processed downstream by stream processing units such as vertex processors, rasterizers, and fragment processors, as discussed above

Point D:

These two guys (Robin J Green & Gabor Nagy) play a key role in Sony development community; they have worked on previous co-sub projects with Sony. Green by the way has worked/still working with EA.

Anyhow, This patent by them (I can 100% guarantee is based around PS3 development) is dealing with a stream processor: "Method and apparatus for real-time global illumination incorporating stream processor based hybrid ray tracing

".

A method for calculating a lighting function for an object to be rendered using a basis function is provided. The method includes calculating a transfer function approximation of the lighting function through a stream processor. A method for presenting lighting characteristics associated with a display object in real-time and a method for determining secondary illumination features for an object to be displayed are also provided. A computer readable medium and a computing device having a graphics processing unit capable of determining lighting characteristics for an object in real time are also included.

1. A method for presenting lighting characteristics associated with a display object in real-time, comprising: executing a ray tracing algorithm through a stream processor, the executing including; generating a ray associated with a point on the display object; and determining an approximation of a transfer function component using at least one basis function.

6. A method for determining secondary illumination features for an object to be displayed, comprising: providing a stream processor capable of identifying a path associated with a ray; generating a ray from a point on the object; determining if the path of the ray intersects a surface; and calculating an approximation to a transfer function associated with at least one basis function, wherein the approximation to the transfer function represents a component of the secondary illumination features

17. A computer readable medium having program instructions for determining secondary illumination features for an object to be displayed, comprising: program instructions for accessing a stream processor capable of identifying a path associated with a ray; program instructions for generating a ray from a point on the object; program instructions for determining if the path of the ray intersects a surface; and program instructions for calculating an approximation to a transfer function associated with at least one basis function, wherein the approximation to the transfer function represents a component of the secondary illumination features.

39. A computing device, comprising: a graphics processing unit (GPU) capable of determining lighting characteristics for an object in real time, the lighting characteristics defined through a basis function, the GPU including a stream processor configured to split a stream of data associated with the lighting characteristics into multiple simultaneous operations.

[0013] Broadly speaking, the present invention fills these needs by providing a method and apparatus that takes advantage of features associated with omni-directional basis functions and stream processing functionality in order to apply ray tracing techniques for lighting calculations. It should be appreciated that the present invention can be implemented in numerous ways, including as a method, a system, computer readable medium or a device. Several inventive embodiments of the present invention are described below.

[0082] As mentioned above, the characteristics of spherical harmonic lighting enable soft shadows to be defined with minimal work. A transfer function defines the surface reflectance so that self transfer components may be represented. Through the use of stream processors, the transfer function may be calculated in real time so that a video game may more realistically define shadows during a presentation. That is, the above embodiments use GPU programs for ray tracing to calculate a SH global illumination solution in object space through a relatively low number of rays per vertex, which effectively performs lighting calculations at each vertex. The resulting spherical harmonic encoded transfer functions are interreflected and rendered using Gouraud shaded triangles to reconstruct the lighting function between the sample points. In another embodiment, the movie industry may apply the embodiments described herein to pre-visualization operations to provide real-time information. As mentioned above, any suitable basis function parametarized over some domain of directions, e.g., a wavelet or an orthonormal basis function may be utilized as the embodiments described herein are not limited to spherical harmonics.

Please constructive feed back of ideals, thoughts, criticism, or just a general take of the subject.

No lame remarks “PO-LEASE” :smile:

Last edited by a moderator: