You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

PlayStation 4 (codename Orbis) technical hardware investigation (news and rumours)

- Thread starter Love_In_Rio

- Start date

- Status

- Not open for further replies.

Bagel seed

Veteran

So now we know what VCE, UVD and DCE was from Sweetvar's info

And microsoft-sony.com was the secret pact to get rid of the GPU :|

Graphic North Bridge(GNB) Highlights

Fusion 1.9 support

DCE 7.0

UVD 4.0

VCE

IOMMU

ACP

5x8 GPP PCIE cores

SCLK 800MHz/LCLK 800MHz

As far as I know.and what I've heard, both PS4 and Xbox 720 have APU+GPU.

Everything being provided by AMD.

And microsoft-sony.com was the secret pact to get rid of the GPU :|

Wouldnt the 4 cu's just be accounting for the apu. Its apu + discrete correct?

this is what says aegis two months ago..

The next Xbox and PlayStation are not "GPU-centric." There are pretty significant things happening with their processor architectures. And at least for Durango, it's not using off the shelf kit, contrary to what many GAF posters have insisted. Even more troublesome for the Wii U, they have much more dedicated GPGPU capabilities which aren't happening on the dedicated GPUs they're packing.

Bagel seed

Veteran

huh? UVD's been around forever. That's the video/media decoder. VCE was introduced with 7970 (Video Codec Engine) for encoding 1080p60 streams. DCE has also just been a part of Radeons. That's just... standard.

Shrugs. Never was an AMD follower.

DJ12 said:So nothing really new from the df article.

Roll on e3 although then we'll have to decipher marketing BS as well.

Well we got the 14+4 which solved a couple mysteries for us. Other than that this slow balloon style leakage shrinking into a puddle of wrinkled latex reality is quite humbling.

bgassassin

Regular

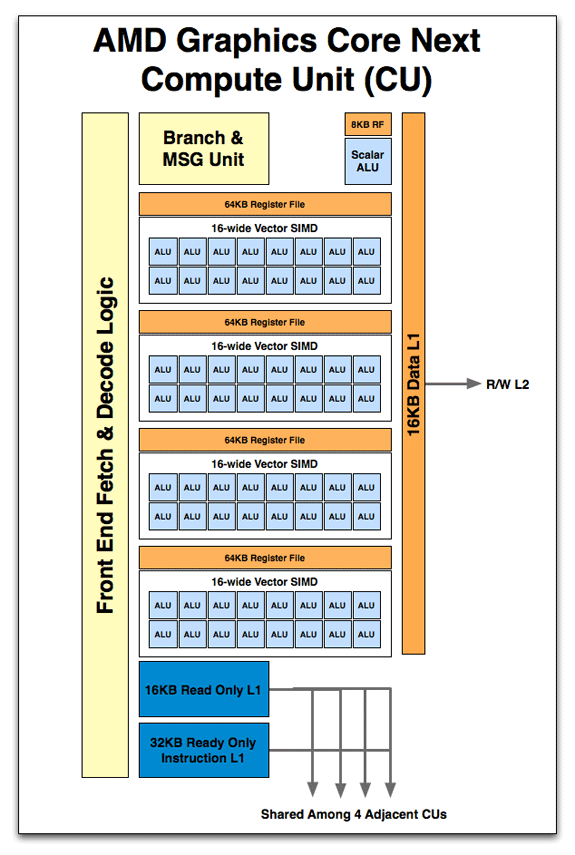

Giving my take on the 14+4 and the wording, how it sound to me is that the 4 CUs have 64+1 ALUs as opposed to the normal 64 in a CU. The +1 is dedicated to compute, but if used for rendering would give a minor boost. For me I would wonder if this "extra" ALU is modified in some manner. Is it the scalar ALU that's already on a CU, but modified? Is it another ALU in addition to that? I would assume that the scalar ALU on a CU is an "understood" and this is some kind of additional ALU.

I believe that extra ALU is for redundancy against manufacturing errors; using it for compute tasks while the rest of the CU renders graphics shouldn't be possible as I believe all ALUs run the same shader program. The penalty for packing so much computing hardware into such a small space is you lose flexibility.how it sound to me is that the 4 CUs have 64+1 ALUs as opposed to the normal 64 in a CU. The +1 is dedicated to compute, but if used for rendering would give a minor boost.

So does this leak tell us absolutely for sure that Orbis does not have a dedicated GPU? I wish we could find out for sure. In my opinion, a dedicated GPU would be what makes one of these consoles something truly amazing. Even if the dedicated GPU was not a high end part, combined with the GPU in the APU you would have two GPUs in the system.

bgassassin

Regular

I believe that extra ALU is for redundancy against manufacturing errors; using it for compute tasks while the rest of the CU renders graphics shouldn't be possible as I believe all ALUs run the same shader program. The penalty for packing so much computing hardware into such a small space is you lose flexibility.

That wouldn't make sense to me since when looking at the description it says it's for compute, not for redundancy.

- 4 additional CUs (410 Gflops) “extra” ALU as resource for compute

Here is a picture of a CU.

Technically a CU has 65 ALUs because of the Scalar ALU. I'm suggesting either that Scalar ALU was modified, or another (possibly custom) ALU was added somewhere.

Bagel seed

Veteran

Maybe this is where the "Scalar ALU's 320" comes in?

320 / 4 = 80

So 80 ALU's per each of the CU's?

That would give an extra 16 ALU

And then 5 SIMD "blocks"

New Starsha GNB 28nm TSMC

Milos

Southern Islands

DX11

SM 5.0

Open CL 1.0

Quad Pixel pipes 4

SIMD’s 5

Texture Units 5TCP/2TCC

Render back ends 2

Scalar ALU’s 320

320 / 4 = 80

So 80 ALU's per each of the CU's?

That would give an extra 16 ALU

And then 5 SIMD "blocks"

bgassassin

Regular

Maybe this is where the "320 Scalar ALU's" comes in?

320 / 4 = 80

So 80 ALU's per each of the CU's?

That would give an extra 16 ALU

Forgot about Sweetvar's info. That would make more sense to me than what I was trying to speculate from a performance perspective as my original idea wasn't suggesting much of a boost. That would mean it should be labeled as an "'extra' SIMD", not ALU. In turn it's the extra SIMD that is dedicated towards compute, but could be used for rendering for a minor boost.

64 ALUs = 102.4 GFLOPs

This could be used for compute or rendering.

Last edited by a moderator:

Bagel seed

Veteran

If it's true then it would indeed explain the minor boost part. We would also be back to our old mighty 18CU setup for rendering.

In that case is it even considered to be enough for extra compute tasks with 1 extra SIMD per CU?

In that case is it even considered to be enough for extra compute tasks with 1 extra SIMD per CU?

bgassassin

Regular

I guess it would depend on what the developer needs. I would assume the dev is free to use more of the CU or CUs for compute if needed.

Bagel seed

Veteran

So the way they should've worded it is, 4 CU's have an extra SIMD (or 16 ALU) dedicated for compute. Can also be used for rendering for a minor boost.

bgassassin

Regular

That or instead of:

it should have been:About 14 + 4 balance:

- 4 additional CUs (410 Gflops) “extra” ALU as resource for compute

- Minor boost if used for rendering

About 14 + 4 balance:

- 4 additional CUs (410 Gflops) with “extra” SIMD as resource for compute

- Minor boost if "extra" SIMDs used for rendering

Last edited by a moderator:

Bagel seed

Veteran

Glad we cracked the case. This is entirely different than what we all thought this morning then, because in no way would 4 CU's (with an extra SIMD to boot) that when also used in rendering be just a "minor boost".

Need less spec sheet regurgitation leak and more knows what's actually going on dev leak

Need less spec sheet regurgitation leak and more knows what's actually going on dev leak

- Status

- Not open for further replies.

Similar threads

- Replies

- 10

- Views

- 3K

- Replies

- 90

- Views

- 13K

- Replies

- 213

- Views

- 22K

- Replies

- 4

- Views

- 2K