http://semiaccurate.com/forums/showpost.php?p=155075&postcount=148

nice sharp .png image.. it would be more credible if it's taken through monitor by a 1MP camera

Look like you was right on the shot.

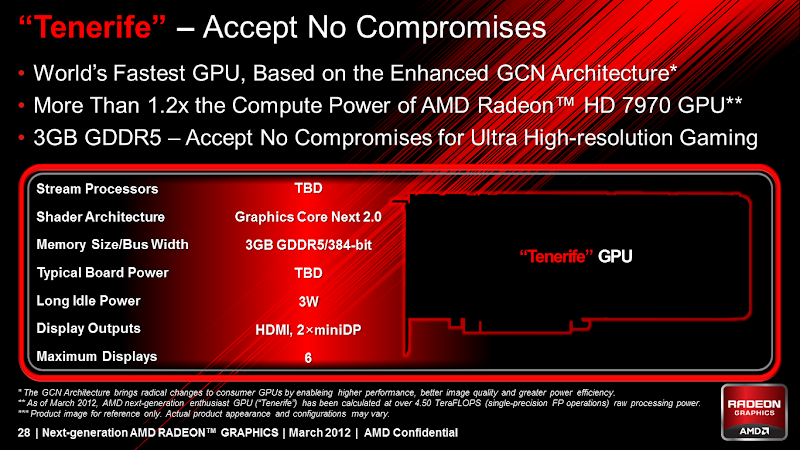

A few days ago in an alleged web AMD presentation slide, which spoke of a coming new AMD GPU, which is conducted under the code name of Tenerife. This should be up to 20 percent more performance compared to previous Tahitian flagship http://translate.googleusercontent...._test/&usg=ALkJrhin1Xmh-TnmrGQPjaDYPupob0dVeQHD7970 bring.

Immediately there was speculation of course, that this would be AMD's answer to the supposedly introduced in the near future NVIDIA-Kepler-series in 28-nm manufacturing. In today's CeBIT meeting with AMD, we talked to Product Manager Evan Groenke on these films. Mr. Groenke knew the film already and could not suppress a grin. He described the film as a well-made fake, and said openly, that this does not constitute an official AMD film. Rather, he assumes that this must be a "fun contemporary" was at work, who have seen the previous naming of the new Graphic-core next-products and some simply picked a name for this island venture out.

http://translate.google.com/transla..._tenerife-gpu_stellen_eine_falschmeldung_dar/