Inuhanyou

Veteran

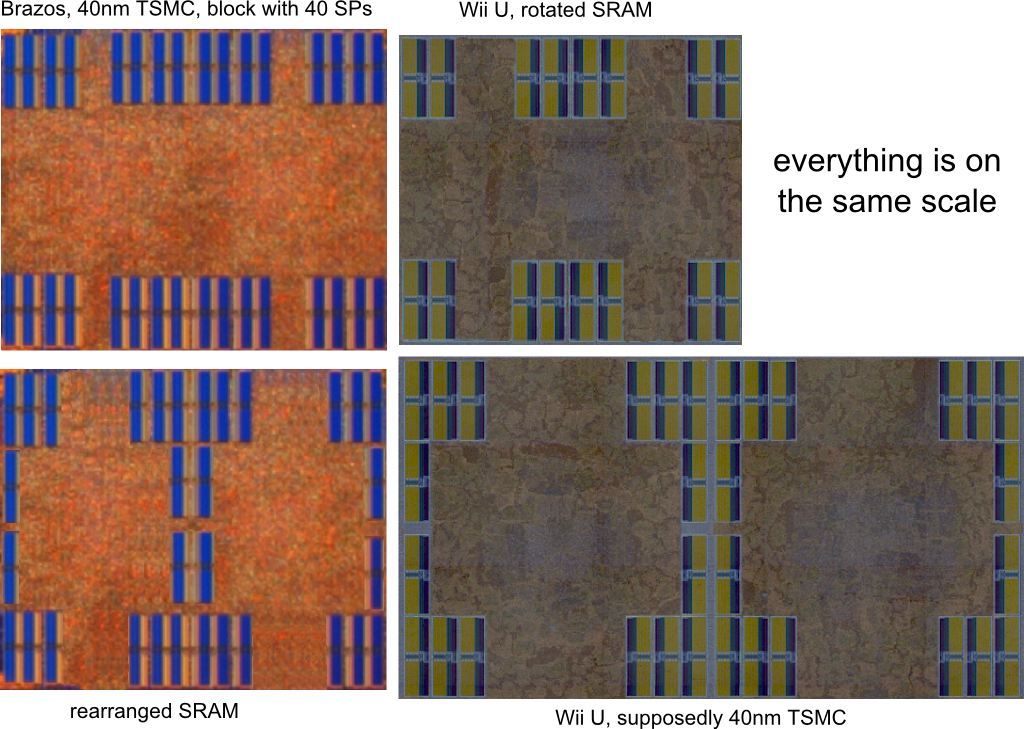

Our technical theories aren't all that technical. 160SPU's just seems like not enough to support what the Wii U has been pushing out. But then 320 would seem like an obvious advantage as well, but we would know it was 320SPU's if that was the case.

Really though, we're going off of barely there fumes.

Really though, we're going off of barely there fumes.