I think lower clocks are better for power drain, while deactivated blocks are better for yields...Additionally, if they really ran into a power wall, higher clocks may be the less advisable choice unless they can really turn the disabled SM(s) completely off.

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

NVIDIA GF100 & Friends speculation

- Thread starter Arty

- Start date

PSU-failure

Newcomer

AFAIK, only intel can do it with bulk processes so far, and AMD can't/won't do it on 45nm or older SOI.

However, power-gating seems to be quite prevalent in the low power devices. I wonder how they do it if power gating transistors are hard to do if you are not Intel.

You just answered to your own question : low power.

It's easier to handle power gating when the power transistor doesn't have to cope with high currents (in the A territory, if not tens of A in the case of a GPU).

DavidGraham

Veteran

Hey Mr.CarstenS , Just noticed your GTX480 Unpacking video !!

http://www.hardwareclips.com/video/250/PCGH-Uncut--Folge-3-Geforce-GTX-480-im-Testlabor

http://www.hardwareclips.com/video/250/PCGH-Uncut--Folge-3-Geforce-GTX-480-im-Testlabor

Hey Mr.CarstenS , Just noticed your GTX480 Unpacking video !!

http://www.hardwareclips.com/video/250/PCGH-Uncut--Folge-3-Geforce-GTX-480-im-Testlabor

We don't know what that is. Like he said in the video, it might just as well be the "weekly nvidia chocolate bar".

DavidGraham

Veteran

Oh you know German ? If so , then I want a taste of that big chocolate bar , could you guide me to where I could get some of it ?We don't know what that is. Like he said in the video, it might just as well be the "weekly nvidia chocolate bar".

The recommended PSU is not really indicative when it comes to TDP... It can be more indicative of the real consumption, maybe...

For example, a 600W PSU (without any recommendation of current ratings) is recommended for a HD5850 crossfire ( http://www.amd.com/us/products/desk...s/ati-radeon-hd-5850-system-requirements.aspx )

On NVidia website there are cards with a lower TDP than others that require a better PSU (9800GX2 vs GTX280, the first has a lower TDP than the latter, but requires an higher rated PSU).

http://www.nvidia.com/object/product_geforce_gtx_280_us.html

http://www.nvidia.com/object/product_geforce_9800_gx2_us.html

It's easier to handle power gating when the power transistor doesn't have to cope with high currents (in the A territory, if not tens of A in the case of a GPU).

Multiple power gate transistors ganged together FTW?

What's preventing that? Certainly not area, especially on 40nm and on >3,000,000,000 transistor dies.

Low power designs probably can afford higher voltage drop on the power gates, both because they rarely power up 100% of the hardware (video playback won't generally be accompanied by heavy UI use for instance) and because they are inherently more judged on average power consumption (ie. battery life). Increasing power consumption for peak use on GPUs is a lot less palatable.

Pity they can't integrate MEMS relays (ie. near 0 voltage drop) with normal ASICs.

Pity they can't integrate MEMS relays (ie. near 0 voltage drop) with normal ASICs.

FenderBender

Newcomer

Low power designs probably can afford higher voltage drop on the power gates, both because they rarely power up 100% of the hardware (video playback won't generally be accompanied by heavy UI use for instance) and because they are inherently more judged on average power consumption (ie. battery life). Increasing power consumption for peak use on GPUs is a lot less palatable.

Pity they can't integrate MEMS relays (ie. near 0 voltage drop) with normal ASICs.

Is it a crazy idea to switch power for the sub-parts of the chip using power relays at the board level and not onchip? You'd need the different parts of the chip to have independent power input pins, but you have lots of distributed power pins already. And switching may not be fast (since the switch signal would have to be sent offchip) but for shutting down an SM or video processor, it may not be a big deal if there was a 1ms switching latency.

aaronspink

Veteran

AFAIK, only intel can do it with bulk processes so far, and AMD can't/won't do it on 45nm or older SOI.

However, power-gating seems to be quite prevalent in the low power devices. I wonder how they do it if power gating transistors are hard to do if you are not Intel.

You can do power gating using normal transistor but at a heavy cost factor. Most low power devices don't actually have on die power gates though and generally rely on things like multiple voltage rails or bias voltages or are designed using ultra-low-leakage processes with LL transistors and rely on clock gating.

AFAIK, Nehalem is the first commercial part to feature power gating.

aaronspink

Veteran

Multiple power gate transistors ganged together FTW?

What's preventing that? Certainly not area, especially on 40nm and on >3,000,000,000 transistor dies.

Area.

Without a dedicated power gate transistor on the process the amount of area you need to support power gating for a given amperage is pretty large. Both the Intel and AMD solutions rely on very low leakage transistor designs with very high current drive with low resistance. When switched off they effectively act like an open but when switched on they effectively act like a short.

So without a dedicated power gate transistor in the process library, you would have to dedicate a significant amount of area to the gating transistors.

aaronspink

Veteran

Is it a crazy idea to switch power for the sub-parts of the chip using power relays at the board level and not onchip? You'd need the different parts of the chip to have independent power input pins, but you have lots of distributed power pins already. And switching may not be fast (since the switch signal would have to be sent offchip) but for shutting down an SM or video processor, it may not be a big deal if there was a 1ms switching latency.

that would require multiple independent top level power grids on die. Would complicate the power delivery on to the die/package as well. Likely require more power pins. It adds a pretty significant cost factor.

Not crazy at all for lower power applications. Except they simply use multiple power regulators instead of relays... Regulators are cheaper, smaller, don't have mechanical parts (reliability) and also allow one to play with voltage in function of speed demands.Is it a crazy idea to switch power for the sub-parts of the chip using power relays at the board level and not onchip?

It may be a bit tricky to scale to high power chips: it's easier to transport a couple of hunderd milliWatts than tens of Watts do distinct area on a die.

Power gating has been all the rage at conferences for at least 3 years, so I doubt Nehalem was the first commercial device to have it. Though it may very well be the first one among high power chips.

Edit: here's a nice example from 2007/2008.

Last edited by a moderator:

The recommended PSU is not really indicative when it comes to TDP... It can be more indicative of the real consumption, maybe...

For example, a 600W PSU (without any recommendation of current ratings) is recommended for a HD5850 crossfire ( http://www.amd.com/us/products/desk...s/ati-radeon-hd-5850-system-requirements.aspx )

On NVidia website there are cards with a lower TDP than others that require a better PSU (9800GX2 vs GTX280, the first has a lower TDP than the latter, but requires an higher rated PSU).

http://www.nvidia.com/object/product_geforce_gtx_280_us.html

http://www.nvidia.com/object/product_geforce_9800_gx2_us.html

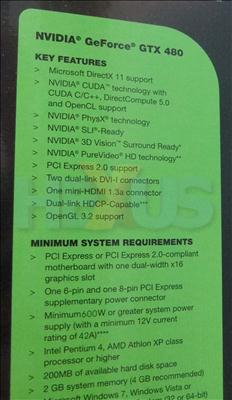

Ok I'll use cliff notes then: GTX480 = 250W TDP.

Multiple power gate transistors ganged together FTW?

What's preventing that? Certainly not area, especially on 40nm and on >3,000,000,000 transistor dies.

The "Power gates" used by Intel and AMD are already many transistors. Think about it, both of them are using *METERS* of transistors to gate off the power.

On dice that are no more than 20mm on a side.

David

Did you come up with this number by adding up all the W's for all the transistors involved in power gating?Think about it, both of them are using *METERS* of transistors to gate off the power.

Must be longer than a 5870 since they used a 5970 for comparison.

What's the point of putting your name on these pictures?

I didn't .It is not my name.

Similar threads

- Replies

- 37

- Views

- 4K

- Replies

- 64

- Views

- 5K

- Replies

- 351

- Views

- 36K