I don't know, apparently der8auer doesn't either. It's likely that because it was an engineering sample and possibly not representative of the final product (as Ian Cutress alluded to) that it provided incorrect information regarding Threadripper.Malo why did amd want it taken down ?

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

Memory and peripheral I/O wiring for TR/Epyc(?)

Beautiful.

So Threadrippers are just Epyc fails? :|

Anarchist4000

Veteran

More of a "glass half full/empty" thing. So much for the Epyc pencil mods!So Threadrippers are just Epyc fails? :|

Possibly, but maybe there is a small controller present that can? Something used for their transparent encryption outside the cores. I'm hesitant to limit that capability to only CPUs because I have a hunch Ryzen and Vega dies are somewhat interchangeable with Infinity. Each chip creates the same SERDES links, but features different memory controllers.

Possibly, although as a slave device there would be classes of issues where Vega would defer to a CPU.

What some of the exception or fault handling would do if data within an encrypted VM was associated with an error that propagated up to the hypervisor is uncertain. It would seemingly constrain some of the tools used to allow systems to manage failures or log data, unless those became a vector for leaking data.

Involving the secure enclave in link errors and calling interrupt/exception code might itself become a vector via bus-glitching or some kind of malicious remote node.

That would scale horribly on just four mem channels.That 4 die Threadripper is such a wind up. I was planning on buying 1950X this autumn. Now I'm wondering if there'll be a 32-core Threadripper. 1999X for Christmas?

I wonder how much more would a X399 motherboard cost with fully wired SR3 socket.

That 4 die Threadripper is such a wind up. I was planning on buying 1950X this autumn. Now I'm wondering if there'll be a 32-core Threadripper. 1999X for Christmas?

Epyc 7551P (at $2100) ?

Cheers

Another possibility claimed to have been disclosed in the following is that the other dies are mechanical placeholders.

http://www.pcworld.com/article/3211...en-threadripper-has-two-mysterious-chips.html

Not much distinguishing detail from a distance and under a solder layer to discern if they are.

http://www.pcworld.com/article/3211...en-threadripper-has-two-mysterious-chips.html

Not much distinguishing detail from a distance and under a solder layer to discern if they are.

hoom

Veteran

Probably depends on how sales go/how hard Intel fights.Now I'm wondering if there'll be a 32-core Threadripper.

Jawed

Legend

That's Gubbi's point.

As far as I can tell the sockets for EPYC and Threadripper are only marginally different. So wiring up and fitting the memory on a consumer mobo is the real question, I suppose. You end up with a server mobo and server processor. So why even make consumer 32 core Threadripper and mobo...

As far as I can tell the sockets for EPYC and Threadripper are only marginally different. So wiring up and fitting the memory on a consumer mobo is the real question, I suppose. You end up with a server mobo and server processor. So why even make consumer 32 core Threadripper and mobo...

He is quite sure that the information pertained therein still is legit. Maybe they want to do yet another double blind test. Like - can you feel the difference in L3 latency...I don't know, apparently der8auer doesn't either. It's likely that because it was an engineering sample and possibly not representative of the final product (as Ian Cutress alluded to) that it provided incorrect information regarding Threadripper.

Anarchist4000

Veteran

Might make sense if the pins were re-purposed for power delivery. Save costs from 4 fewer memory channels, but leave open the possibility of other accelerators with integrated memory: FPGAs, DSPs, GPUs, stacked DRAM, etc. That would follow their heterogeneous capabilities when Epyc with 128 PCIE lanes was overkill. Threadripper ITX platform, with a dozen USB3.1 ports, Thunderbolt, dual 10GbE networks, etc that wouldn't be excessive at all.As far as I can tell the sockets for EPYC and Threadripper are only marginally different. So wiring up and fitting the memory on a consumer mobo is the real question, I suppose. You end up with a server mobo and server processor. So why even make consumer 32 core Threadripper and mobo...

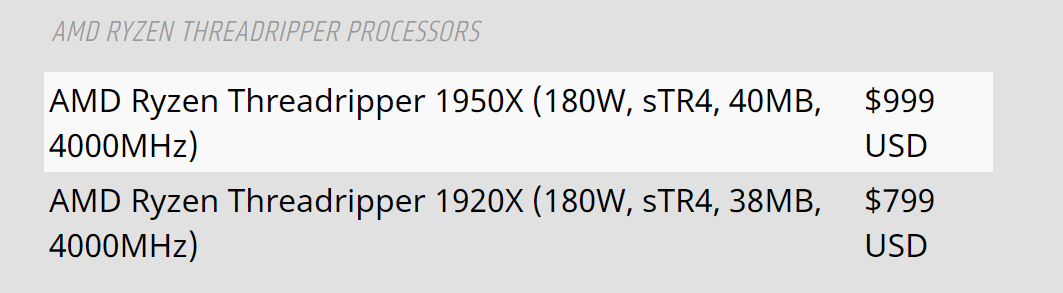

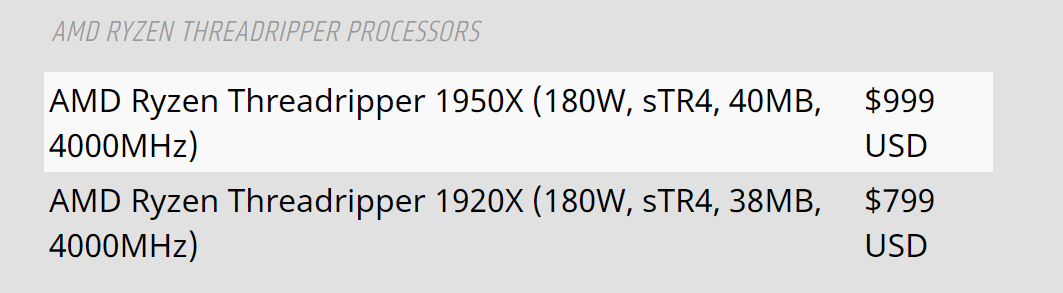

https://www.amd.com/Documents/AMD-Product-Master.pdf

via https://www.planet3dnow.de/cms/3314...p-b1-somit-kein-teildeaktivierter-epyc-zp-b2/

6 Threadripper models, 1900(X), 1920(X), 1950(X).

TDP different between non-X and X-models

All of them use Zeppelin B1-stepping while Epyc uses B2-stepping

via https://www.planet3dnow.de/cms/3314...p-b1-somit-kein-teildeaktivierter-epyc-zp-b2/

6 Threadripper models, 1900(X), 1920(X), 1950(X).

TDP different between non-X and X-models

All of them use Zeppelin B1-stepping while Epyc uses B2-stepping

Can I make an semi-oftipic question?

How ryzen 3 1200 compare against an old i5 4590?

Enviado desde mi 2PS64 mediante Tapatalk

It's close to an i5-2500K, so probably close to that too:

http://www.hardware.fr/articles/966-4/performances-applicatives.html

Interesting, TR parts will have more than twice the cache of R7 CPUs: https://videocardz.com/newz/amd-confirms-tdp-and-cache-of-ryzen-threadripper

How is that possible when using two Zeppelin dies? 2x would put them at 32mb, 40mb is a 25% increase over that.

Edit: They must be counting L2 + L3 for that to make sense. 32mb L3 + 8/6 mb L2

How is that possible when using two Zeppelin dies? 2x would put them at 32mb, 40mb is a 25% increase over that.

Edit: They must be counting L2 + L3 for that to make sense. 32mb L3 + 8/6 mb L2

Similar threads

- Replies

- 90

- Views

- 13K

- Replies

- 220

- Views

- 87K

- Locked

- Replies

- 24

- Views

- 14K

- Replies

- 601

- Views

- 88K